FUNCTIONAL DESCRIPTION

MACHINE

CYCLE

STATUS

CONTROL

101M

S1

so

RD

WR

INTA

OPCODE FETCH

(OF)

0

1

1

0

1 1

MEMORY READ

(MR)

0 1 0

0

1 1

MEMORY WRITE

(MW)

0 0 1

1

0

1

1/0

READ

(lOR)

1 1 0

0

1 1

110

WRITE

(lOW)

1 0 1

1

0 1

INTR ACKNOWLEDGE

(INA)

1 1 1

1

1

0

BUS

IDLE

(81l:

DAD

0 1 0 1 1 1

INA(RST/TRAP) 1 1

1

1

1.

1

HALT

TS

0 0

TS TS

1

O=Logic"O"

1=Logic"1"

TS=High

Impedance

X=Unspecified

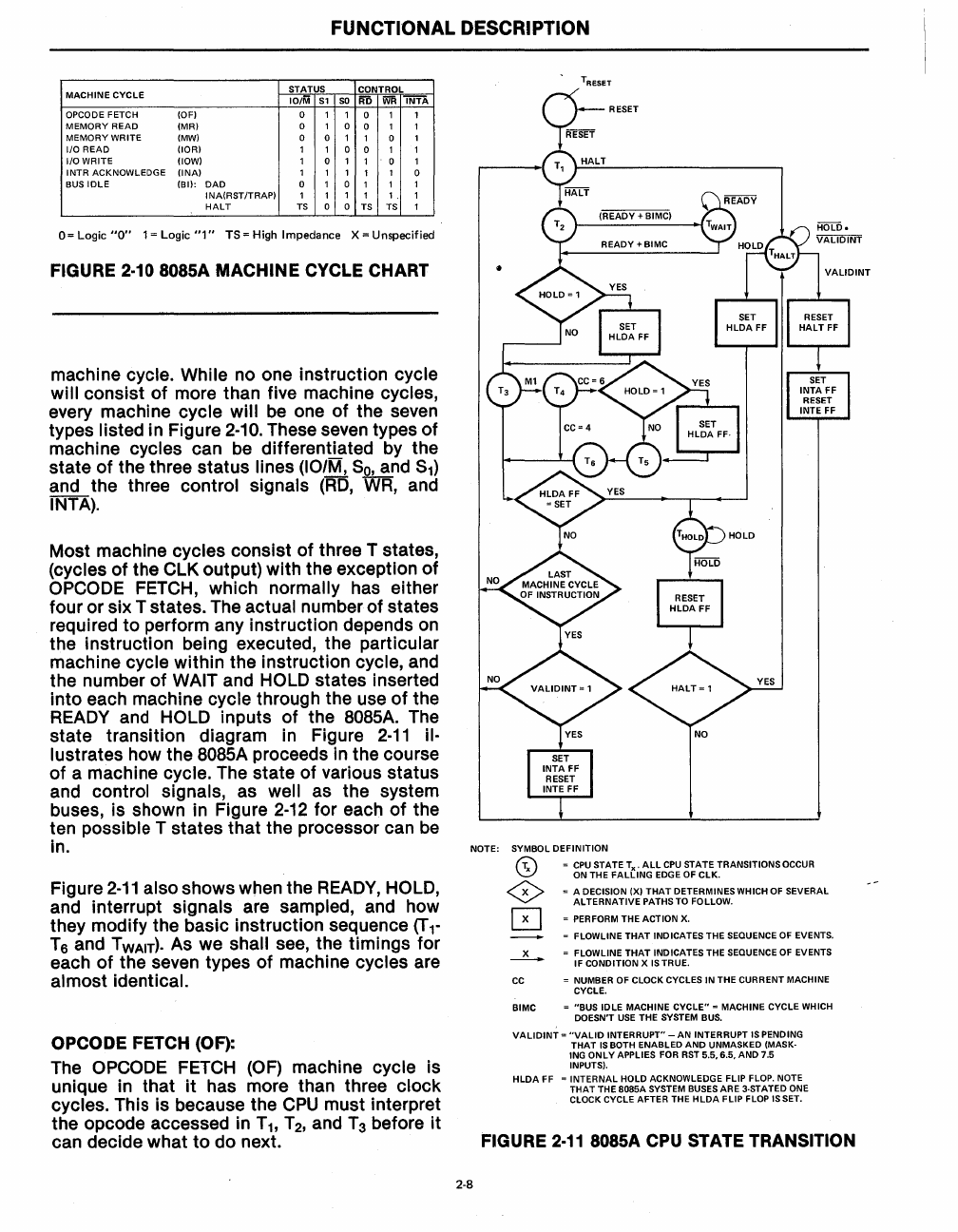

FIGURE 2·10 808SA

MACHINE

CYCLE CHART

machine

cycle. While no one instruction cycle

will

consist of more than five machine cycles,

every machine cycle will be one of the seven

types

listed

in

Figure

2-10.

These seven types of

machine

cycles can be differentiated

by

the

state of the three status

lines

(101M,

5.9.L!.nd

51)

and the three control signals (RD, WR, and

INTA).

Most machine cycles consist of three T states,

(cycles of the

ClK

output) with the exception of

OPCODE FETCH, which normally has either

four or six T states. The

actual number of states

required to perform any instruction depends

on

the instruction being executed, the particular

machine

cycle within the instruction cycle, and

the number of

WAIT and HOLD states inserted

into each machine

cycle through the use of the

READY and

HOLD inputs of the

BOB5A.

The

state transition diagram

in

Figure

2-11

il-

lustrates

how the

BOB5A

proceeds

in

the course

of a machine

cycle. The state of various status

and

control signals, as well as the system

buses,

is

shown

in

Figure

2-12

for each of the

ten

possible T states that the processor can be

in.

Figure

2-11

also shows when the READY, HOLD,

and interrupt signals are sampled, and how

they modify the basic instruction sequence

(T

1-

T 6 and T WAIT). As we shall see, the timings for

each of the seven types of machine

cycles are

almost identical.

OPCODE

FETCH (OF):

The OPCODE FETCH (OF) machine cycle

is

unique

in

that it has more than three clock

cycles.

This is because the CPU must interpret

the opcode accessed

in

Th

T

2

,

and

T3

before it

can decide what to do next.

NOTE: SYMBOL

DEFINITION

2-8

fT,;\

=

CPU

STATE

Tx'

ALL

CPU

STATE TRANSITIONS OCCUR

~

ON THE

FALLING

EDGE

OF CLK.

~

= A DECISION (X)

THAT

DETERMINES WHICH

OF

SEVERAL

~

ALTERNATIVE

PATHS TO FOLLOW.

o = PERFORM THE ACTION

X.

CC

= FLOWLINE

THAT

INDICATES THE SEQUENCE OF EVENTS.

= FLOWLINE

THAT

INDICATES THE SEQUENCE OF EVENTS

IF CONDITION

X

IS

TRUE.

= NUMBER

OF

CLOCK CYCLES

IN

THE CURRENT MACHINE

CYCLE.

BIMC = "BUS IDLE MACHINE

CYCLE"

= MACHINE CYCLE WHICH

DOESN'T

USE

THE SYSTEM BUS.

VALIDINT

=

"VALID

INTERRUPT" -

AN

INTERRUPT

IS

PENDING

THAT

IS

BOTH ENABLED

AND

UNMASKED (MASK·

ING

ONLY

APPLIES FOR RST 5.5, 6.5,

AND

7.5

INPUTS).

HLDA

FF =

INTERNAL

HOLD ACKNOWLEDGE FLIP FLOP. NOTE

THAT

THE

BOB5A

SYSTEM BUSES ARE 3·STATED ONE

CLOCK

CYCLE AFTER THE

HLDA

FLIP FLOP ISSET.

FIGURE

2·11

808SA CPU STATE TRANSITION