107 www.national.com

CP3BT26

TFWL The Transmit FIFO Warning Limit bits specify

how many more bytes can be transmitted from

the respective FIFO before an underrun con-

dition occurs. If the number of bytes remaining

in the FIFO is equal to or less than the select-

ed warning limit, the TXWARN bit in the

FWEV register is set. To avoid interrupts

caused by setting this bit while the FIFO is be-

ing filled before a transmission begins, TX-

WARN is only set when transmission from the

endpoint is enabled (TX_ENn in the TXCn

register is set). See Table 43.

IGN_ISOMSK

The Ignore ISO Mask bit has an effect only if

the endpoint is set to be isochronous. If set,

this bit disables locking of specific frame num-

bers with the alternate function of the TOG-

GLE bit. Therefore, data is transmitted upon

reception of the next IN token. If clear, data is

only transmitted when FNL0 matches TOG-

GLE. This bit is cleared after reset.

0 – Data transmitted only when FNL0 match-

es TOGGLE.

1 – Locking of frame numbers disabled.

18.3.34 Transmit Data Register n (TXDn)

Each transmit FIFO has one TXDn register. Data written to

the TXDn register is loaded into the transmit FIFO n at the

current location of the transmit write pointer. The TXDn reg-

isters provide write-only access from the CPU bus.

TXFD The Transmit FIFO Data Byte is used to load

the transmit FIFO. Software is expected to

write only the packet payload data. The PID

and CRC16 are inserted automatically in the

transmit data stream.

18.3.35 Receive Status Register n (RXSn)

Each receive endpoint pipe (2, 4, and 6) has one RXSn reg-

ister with the bits defined below. To allow a SETUP packet

to be received after a zero length OUT packet is received,

hardware contains two copies of this register. One holds the

receive status of a zero length packet, and another holds the

status of the next SETUP packet with data. If a zero length

packet is followed by a SETUP packet, the first read of this

register indicates the zero-length packet status, and the

second read, the SETUP packet status. This register pro-

vides read-only access from the CPU bus. After reset it is

clear.

RCOUNT The Receive Counter holds the number of

bytes presently in the endpoint receive FIFO.

If this number is greater than 15, a value of 15

is actually reported.

RX_LAST The Receive Last Bytes bit indicates that an

ACK was sent on completion of a successful

receive operation. This bit is cleared when this

register is read.

0 – No ACK was sent.

1 – An ACK was sent.

TOGGLE The function of the Toggle bit differs depend-

ing on whether ISO or non-ISO operation is

used (as controlled by the ISO bit in the EPCn

register).

Non-Isochronous mode

—A value of 0 in-

dicates that the last successfully received

packet had a DATA0 PID, while a value of

1 indicates that this packet had a DATA1

PID.

Non-Isochronous mode

—This bit reflects

the LSB of the frame number (FNL0) after

a packet was successfully received for this

endpoint.

This bit is cleared by reading the RXSn regis-

ter.

SETUP The Setup bit indicates that the setup packet

has been received. This bit is cleared when

this register is read.

0 – Setup packet has not been received.

1 – Setup packet has been received.

RX_ERR The Receive Error indicates a media error,

such as bit-stuffing or CRC. If this bit is set,

software must flush the respective FIFO.

0 – No receive error occurred.

1 – Receive error occurred.

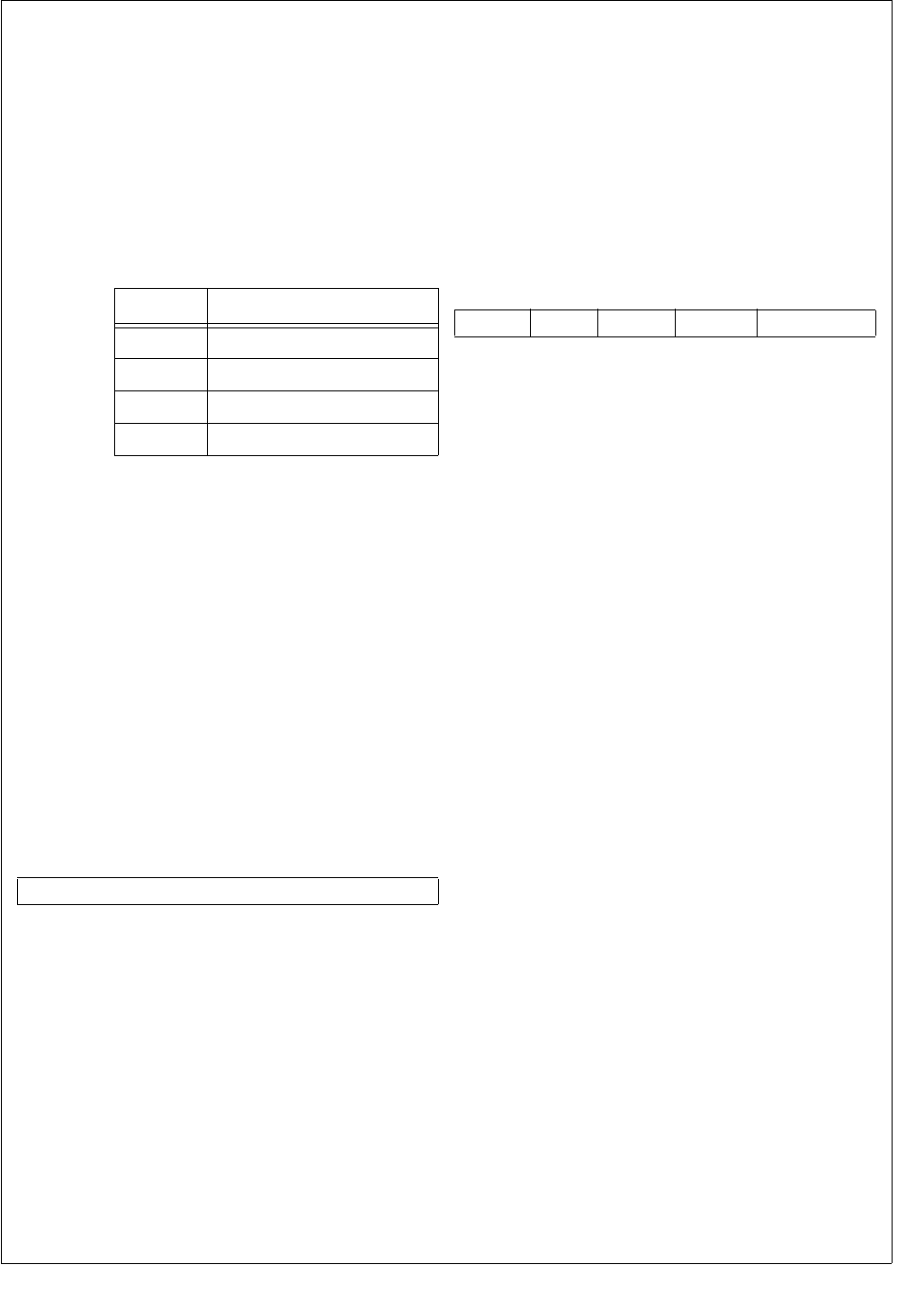

Table 43 Transmit FIFO Warning Limit

TFWL Bytes Remaining in FIFO

00 TFWL disabled

01 ≤ 4

10 ≤ 8

11 ≤ 16

7 0

TXFD

7 6 5 4 3 0

RX_ERR SETUP TOGGLE RX_LAST RCOUNT