117 www.national.com

CP3BT26

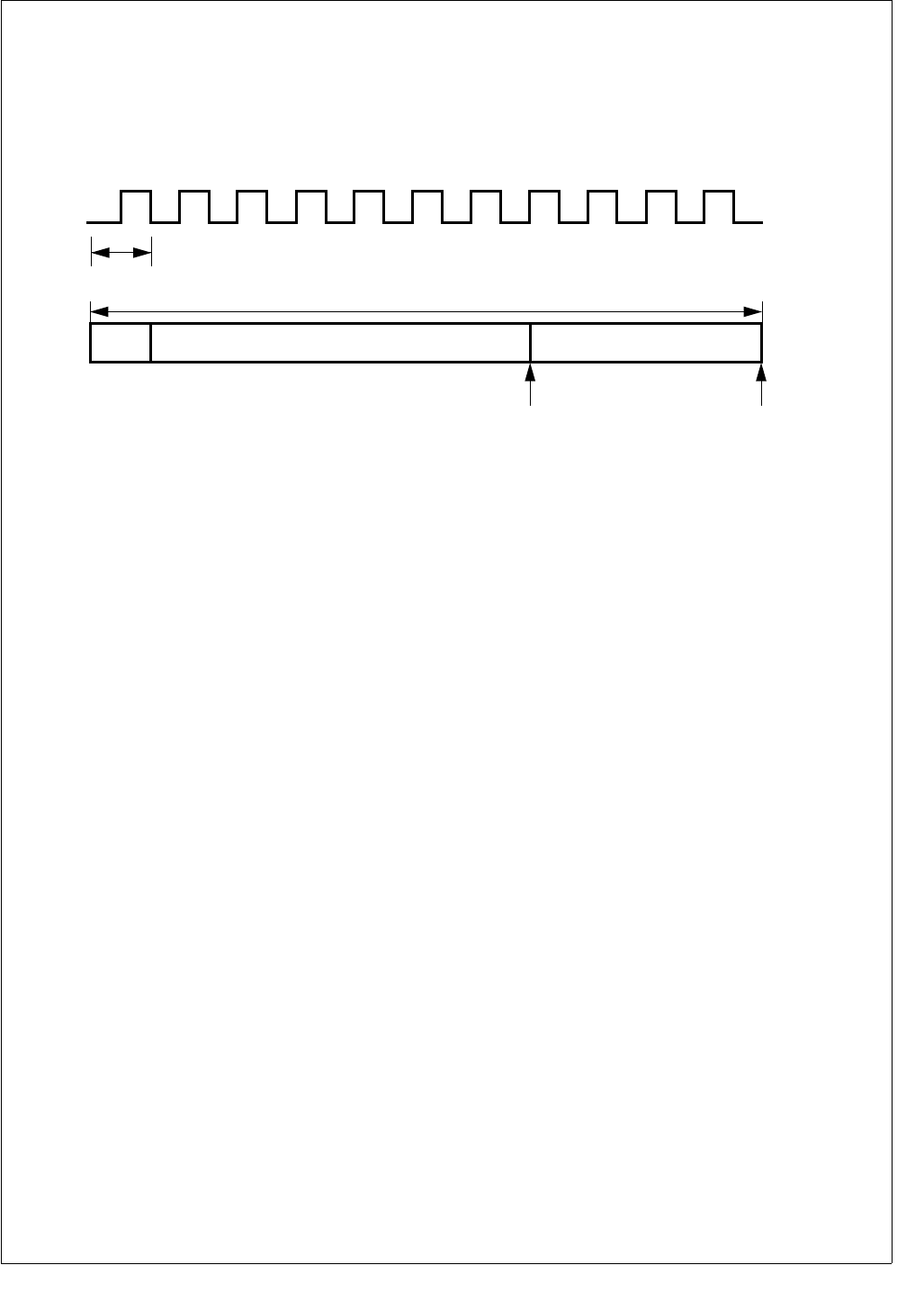

19.2.6 Bit Time Logic

In the Bit Time Logic (BTL), the CAN bus speed and the

Synchronization Jump Width can be configured by software.

The CAN module divides a nominal bit time into three time

segments: synchronization segment, time segment 1

(TSEG1), and time segment 2 (TSEG2). Figure 44 shows

the various elements of a CAN bit time.

CAN Bit Time

The number of time quanta in a CAN bit (CAN Bit Time)

ranges between 4 and 25. The sample point is positioned

between TSEG1 and TSEG2 and the transmission point is

positioned at the end of TSEG2.

Figure 44. Bit Timing

TSEG1 includes the propagation segment and the phase

segment 1 as specified in the CAN specification 2.0B. The

length of the time segment 1 in time quanta (tq) is defined

by the TSEG1[3:0] bits.

TSEG2 represents the phase segment 2 as specified in the

CAN specification 2.0B. The length of time segment 2 in

time quanta (tq) is defined by the TSEG2[3:0] bits.

The Synchronization Jump Width (SJW) defines the maxi-

mum number of time quanta (tq) by which a received CAN

bit can be shortened or lengthened in order to achieve re-

synchronization on “recessive” to “dominant” data transi-

tions on the bus. In the CAN implementation, the SJW must

be configured less or equal to TSEG1 or TSEG2, whichever

is smaller.

Synchronization

A CAN device expects the transition of the data signal to be

within the synchronization segment of each CAN bit time.

This segment has the fixed length of one time quantum.

However, two CAN nodes never operate at exactly the same

clock rate, and the bus signal may deviate from the ideal

waveform due to the physical conditions of the network (bus

length and load). To compensate for the various delays with-

in a network, the sample point can be positioned by pro-

gramming the length of TSEG1 and TSEG2 (see

Figure 44).

In addition, two types of synchronization are supported. The

BTL logic compares the incoming edge of a CAN bit with the

internal bit timing. The internal bit timing can be adapted by

either hard or soft synchronization (re-synchronization).

Hard synchronization is performed at the beginning of a new

frame with the falling edge on the bus while the bus is idle.

This is interpreted as the SOF. It restarts the internal logic.

Soft synchronization is performed during the reception of a

bit stream to lengthen or shorten the internal bit time. De-

pending on the phase error (e), TSEG1 may be increased

or TSEG2 may be decreased by a specific value, the resyn-

chronization jump width (SJW).

The phase error is given by the deviation of the edge to the

SYNC segment, measured in CAN clocks. The value of the

phase error is defined as:

e = 0, if the edge occurs within the SYNC segment

e > 0, if the edge occurs within TSEG1

e < 0, if the edge occurs within TSEG2 of the previous

bit

Resynchronization is performed according to the following

rules:

If the magnitude of e is less then or equal to the pro-

grammed value of SJW, resynchronization will have the

same effect as hard synchronization.

If e > SJW, TSEG1 will be lengthened by the value of the

SJW (see Figure 45).

If e < -SJW, TSEG2 will be shortened by the value SJW

(see Figure 46).

1 to 8 Time Quanta2 to 16 Time Quanta

4 to 25 TIme Quanta

SAMPLE

POINT

TRANSMISSION

POINT

INTERNAL

TIME QUANTA

CLOCK

ONE TIME QUANTUM

16 TIme

Quanta

A TIME SEGMENT 1 (TSEG1) TIME SEGMENT 1 (TSEG1)

A = synchronization segment (Sync)

DS028