www.national.com 200

CP3BT26

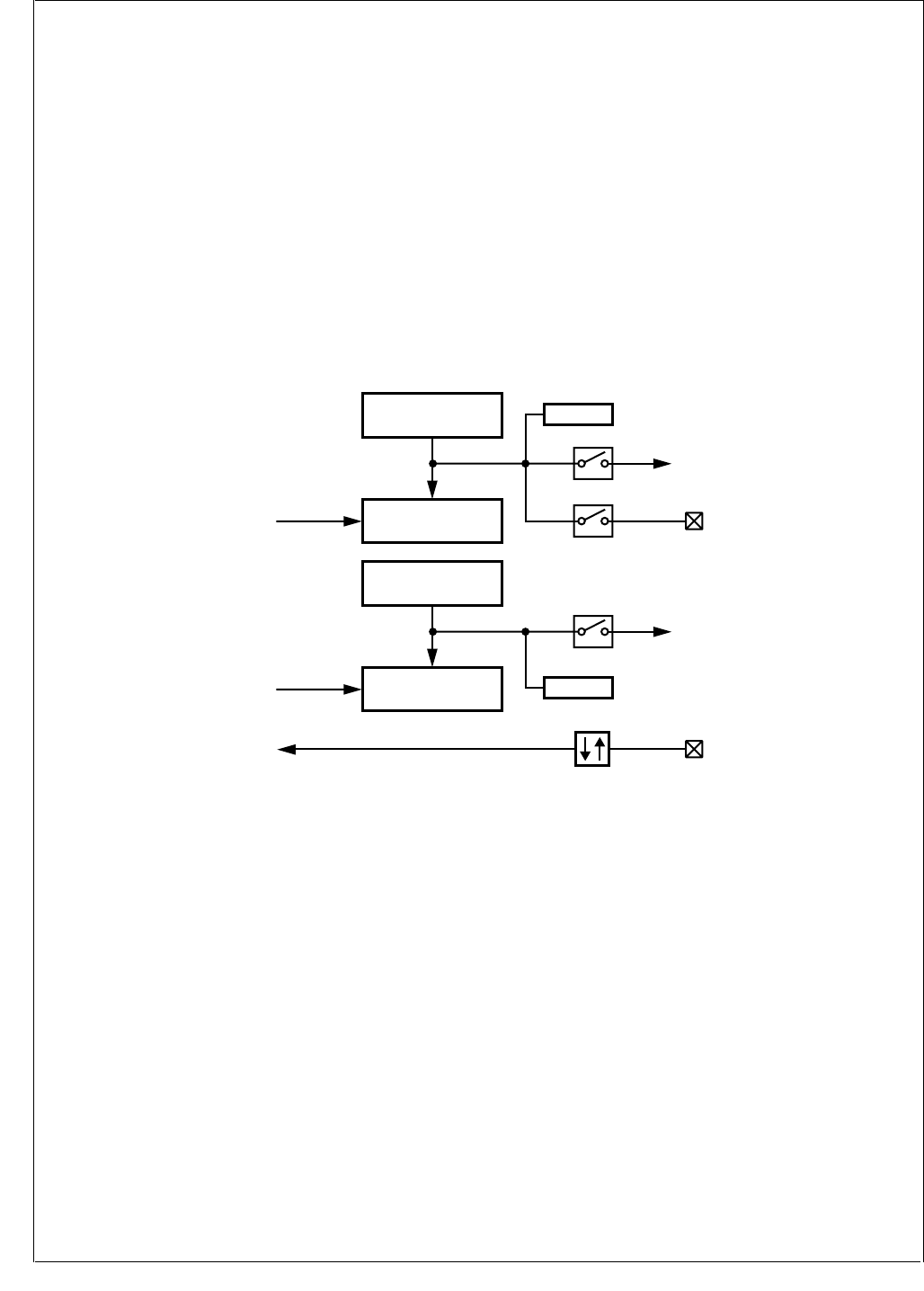

26.2.3 Mode 3: Dual Independent Timer/Counter

Mode 3 is the Dual Independent Timer mode, which gener-

ates system timing signals or counts occurrences of exter-

nal events.

Figure 102 is a block diagram of the Multi-Function Timer

configured to operate in Mode 3. The timer is configured to

operate as a dual independent system timer or dual external

event counter. In addition, Timer/Counter 1 can generate a

50% duty cycle PWM signal on the TA pin. The TB pin can

be used as an external event input or pulse-accumulate in-

put and can be used as the clock source for either Timer/

Counter 1 or Timer/Counter 2. Both counters can also be

clocked by the prescaled System Clock.

Timer/Counter 1 (TCNT1) counts down at the rate of the se-

lected clock. On underflow, it is reloaded from the TCRA

register and counting proceeds down from the reloaded val-

ue. In addition, the TA pin is toggled on each underflow if this

function is enabled by the TAEN bit. The initial state of the

TA pin is software-programmable. When the TA pin is tog-

gled from low to high, it sets the TCPND interrupt pending

bit and also generates an interrupt if enabled by the TAIEN

bit.

Because the TA pin toggles on every underflow, a 50% duty

cycle PWM signal can be generated on the TA pin without

any further action from the CPU.

Timer/Counter 2 (TCNT2) counts down at the rate of the se-

lected clock. On underflow, it is reloaded from the TCRB

register and counting proceeds down from the reloaded val-

ue. In addition, each underflow sets the TDPND interrupt

pending bit and generates an interrupt if the interrupt is en-

abled by the TDIEN bit.

Figure 102. Dual-Independent Timer/Counter Mode

Timer/Counter 1

TCNT1

Timer 1

Clock

Reload A

TCRA

TAPND

TAIEN

Timer

Interrupt 1

TAEN

TA

TB

Underflow

Timer/Counter 2

TCNT2

Timer 2

Clock

Reload B

TCRB

TDPND

TDIEN

Timer

Interrupt 2

Underflow

Clock

Selector

DS086