205 www.national.com

CP3BT26

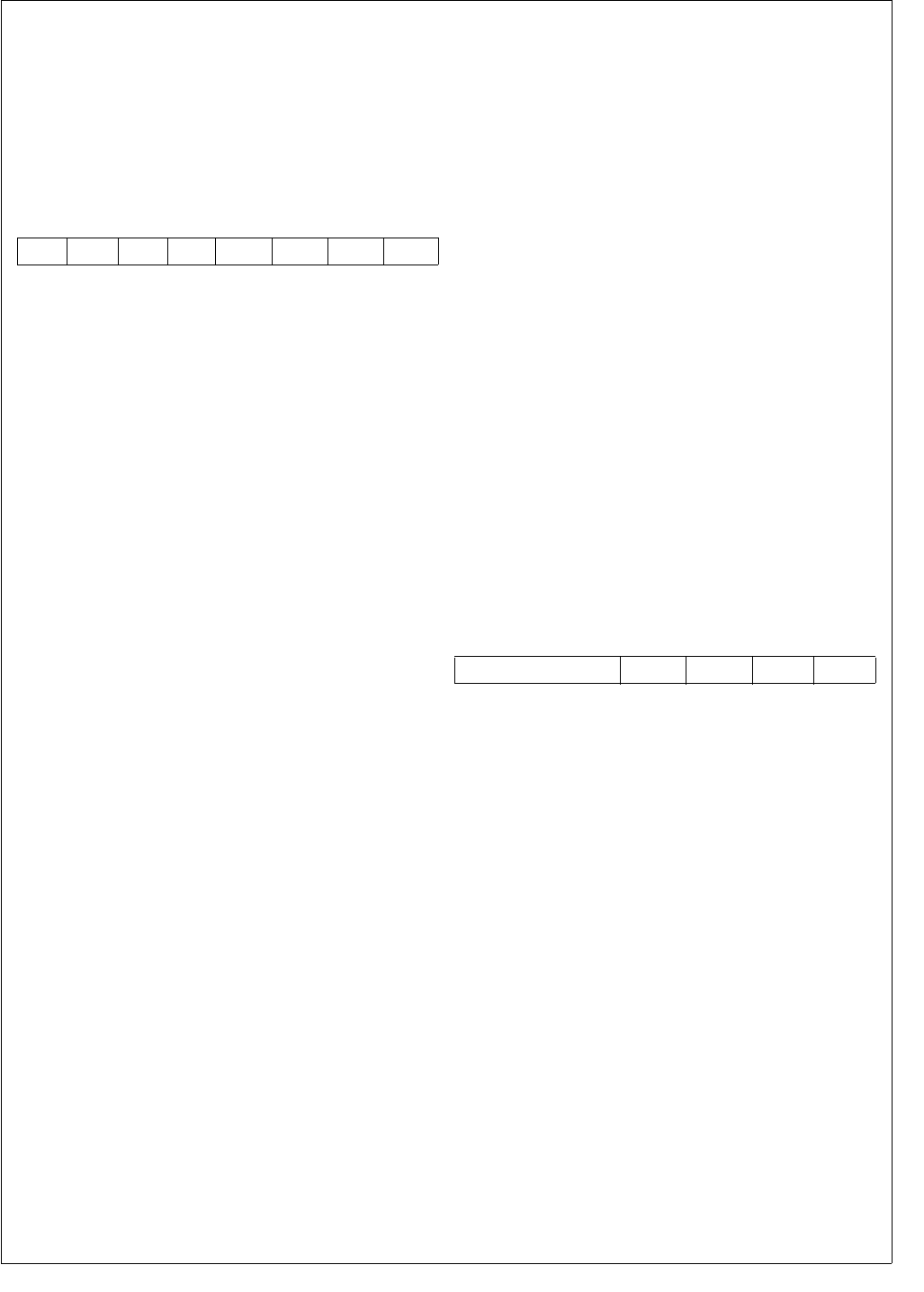

26.5.8 Timer Interrupt Control Register (TICTL)

The TICTL register is a byte-wide, read/write register that

contains the interrupt enable bits and interrupt pending bits

for the four timer interrupt sources, designated A, B, C, and

D. The condition that causes each type of interrupt depends

on the operating mode, as shown in Table 77.

This register is cleared upon reset. The register format is

shown below.

TAPND The Timer Interrupt Source A Pending bit indi-

cates that timer interrupt condition A has oc-

curred. For an explanation of interrupt

conditions A, B, C, and D, see Table 77. This

bit can be set by hardware or by software. To

clear this bit, software must use the Timer In-

terrupt Clear Register (TICLR). Attempting to

directly write a 0 to this bit is ignored.

0 – Interrupt source A has not triggered.

1 – Interrupt source A has triggered.

TBPND The Timer Interrupt Source B Pending bit indi-

cates that timer interrupt condition B has oc-

curred. For an explanation of interrupt

conditions A, B, C, and D, see Table 77. This

bit can be set by hardware or by software. To

clear this bit, software must use the Timer In-

terrupt Clear Register (TICLR). Attempting to

directly write a 0 to this bit is ignored.

0 – Interrupt source B has not triggered.

1 – Interrupt source B has triggered.

TCPND The Timer Interrupt Source C Pending bit in-

dicates that timer interrupt condition C has oc-

curred. For an explanation of interrupt

conditions A, B, C, and D, see Table 77. This

bit can be set by hardware or by software. To

clear this bit, software must use the Timer In-

terrupt Clear Register (TICLR). Attempting to

directly write a 0 to this bit is ignored.

0 – Interrupt source C has not triggered.

1 – Interrupt source C has triggered.

TDPND The Timer Interrupt Source D Pending bit in-

dicates that timer interrupt condition D has oc-

curred. For an explanation of interrupt

conditions A, B, C, and D, see Table 77. This

bit can be set by hardware or by software. To

clear this bit, software must use the Timer In-

terrupt Clear Register (TICLR). Attempting to

directly write a 0 to this bit is ignored.

0 – Interrupt source D has not triggered.

1 – Interrupt source D has triggered.

TAIEN The Timer Interrupt A Enable bit controls

whether an interrupt is generated on each oc-

currence of interrupt condition A. For an ex-

planation of interrupt conditions A, B, C, and

D, see Table 77.

0 – Condition A interrupts disabled.

1 – Condition A interrupts enabled.

TBIEN The Timer Interrupt B Enable bit controls

whether an interrupt is generated on each oc-

currence of interrupt condition B. For an ex-

planation of interrupt conditions A, B, C, and

D, see Table 77.

0 – Condition B interrupts disabled.

1 – Condition B interrupts enabled.

TCIEN The Timer Interrupt C Enable bit controls

whether an interrupt is generated on each oc-

currence of interrupt condition C. For an ex-

planation of interrupt conditions A, B, C, and

D, see Table 77.

0 – Condition C interrupts disabled.

1 – Condition C interrupts enabled.

TDIEN The Timer Interrupt D Enable bit controls

whether an interrupt is generated on each oc-

currence of interrupt condition D. For an ex-

planation of interrupt conditions A, B, C, and

D, see Table 77.

0 – Condition D interrupts disabled.

1 – Condition D interrupts enabled.

26.5.9 Timer Interrupt Clear Register (TICLR)

The TICLR register is a byte-wide, write-only register that al-

lows software to clear the TAPND, TBPND, TCPND, and

TDPND bits in the Timer Interrupt Control (TICTRL) regis-

ter. Do not modify this register with instructions that access

the register as a read-modify-write operand, such as the bit

manipulation instructions. The register reads as FFh. The

register format is shown below.

TACLR The Timer Pending A Clear bit is used to clear

the Timer Interrupt Source A Pending bit

(TAPND) in the Timer Interrupt Control regis-

ter (TICTL).

0 – Writing a 0 has no effect.

1 – Writing a 1 clears the TAPND bit.

TBCLR The Timer Pending A Clear bit is used to clear

the Timer Interrupt Source B Pending bit (TB-

PND) in the Timer Interrupt Control register

(TICTL).

0 – Writing a 0 has no effect.

1 – Writing a 1 clears the TBPND bit.

TCCLR The Timer Pending C Clear bit is used to clear

the Timer Interrupt Source C Pending bit

(TCPND) in the Timer Interrupt Control regis-

ter (TICTL).

0 – Writing a 0 has no effect.

1 – Writing a 1 clears the TCPND bit.

TDCLR The Timer Pending D Clear bit is used to clear

the Timer Interrupt Source D Pending bit (TD-

PND) in the Timer Interrupt Control register

(TICTL).

0 – Writing a 0 has no effect.

1 – Writing a 1 clears the TDPND bit.

7 6 5 4 3 2 1 0

TDIEN TCIEN TBIEN TAI EN TDPND TCPND TBPND TA PN D

7 4 3 2 1 0

Reserved TDCLR TCCLR TBCLR TACLR