141 www.national.com

CP3BT26

The critical path derives from receiving a remote frame,

which triggers the transmission of one or more data frames.

There are a minimum of four bit times in-between two con-

secutive frames. These bit times start at the validation point

of received frame (reception of 6th EOF bit) and end at the

earliest possible transmission start of the next frame, which

is after the third intermission bit at 100% burst bus load.

These four bit times have to be set in perspective with the

timing requirements of the CAN module.

The minimum duration of the four CAN bit times is deter-

mined by the following Bit Time Logic settings:

PSC = PSCmin = 2

TSEG1 = TSEG1min = 2

TSEG2 = TSEG2min = 1

Bit time = Sync + Time Segment 1 + Time Segment 2

= (1 + 2 + 1) tq = 4 tq

= (4 tq × PSC) clock cycles

= (4 tq × 2) clock cycles = 8 clock cycles

For these minimum BTL settings, four CAN bit times take 32

clock cycles.

The following is an example that assumes typical case:

Minimum BTL settings

Reception and copy of a remote frame

Update of one buffer from TX_RTR

Schedule of one buffer from transmit

As outlined in Table 65, the copy process, update, and

scheduling the next transmission gives a total of 17 + 3 + 2

= 22 clock cycles. Therefore under these conditions there is

no timing restriction.

The following example assumes the worst case:

Minimum BTL settings

Reception and copy of a remote frame

Update of the 14 remaining buffers from TX_RTR

Schedule of one buffer for transmit

All these actions in total require 17 + (14 × 3) + 2 = 61 clock

cycles to be executed by the CAN module. This leads to the

limitation of the Bit Time Logic of 61 / 4 = 15.25 clock cycles

per CAN bit as a minimum, resulting in the minimum clock

frequencies listed below. (The frequency depends on the

desired baud rate and assumes the worst case scenario

can occur in the application.)

Table 66 gives examples for the minimum clock frequency in

order to ensure proper functionality at various CAN bus

speeds.

19.11.4 Bit Time Logic Calculation Examples

The calculation of the CAN bus clocks using CKI = 16 MHz

is shown in the following examples. The desired baud rate

for both examples is 1 Mbit/s.

Example 1

PSC = PSC[5:0] + 2 = 0 + 2 = 2

TSEG1 = TSEG1[3:0] + 1 = 3 + 1 = 4

TSEG2 = TSEG2[2:0] + 1 = 2 + 1 = 3

SJW = TSEG2 = 3

Sample point positioned at 62.5% of bit time

Bit time = 125 ns × (1 + 4 + 3 ± 3) = (1 ± 0.375) µs

Bus Clock = 16 MHz / (2 × (1 + 4 + 3)) = 1 Mbit/s (nomi-

nal)

Example 2

PSC = PSC[5:0] + 1 = 2 + 2 = 4

TSEG1 = TSEG1[3:0] + 1 = 1 + 1 = 2

TSEG2 = TSEG2[2:0] + 1 = 0 + 1 = 1

SJW = TSEG2 = 1

Sample point positioned at 75% of bit time

Bit time = 250 ns × (1 + 2 + 1 ± 1) = (1 ± 0.25) µs

Bus Clock = 16 MHz / (2 × (1 + 4 + 3)) = 1Mbit/s (nominal)

19.11.5 Acceptance Filter Considerations

The CAN module provides two acceptance filter masks

GMSK and BMSK, as described in “Acceptance Filtering”

on page 119, “Global Mask Register (GMSKB/GMSKX)” on

page 136, and “Basic Mask Register (BMSKB/BMSKX)” on

page 137. These masks allow filtering of up to 32 bits of the

message object, which includes the standard identifier, the

extended identifier, and the frame control bits RTR, SRR,

and IDE.

19.11.6 Remote Frames

Remote frames can be automatically processed by the CAN

module. However, to fully enable this feature, the RTR/

XRTR bits (for both standard and extended frames) within

the BMSK and/or GMSK register need to be set to “don’t

care”. This is because a remote frame with the RTR bit set

should trigger the transmission of a data frame with the RTR

bit clear and therefore the ID bits of the received message

need to pass through the acceptance filter. The same ap-

plies to transmitting remote frames and switching to receive

the corresponding data frames.

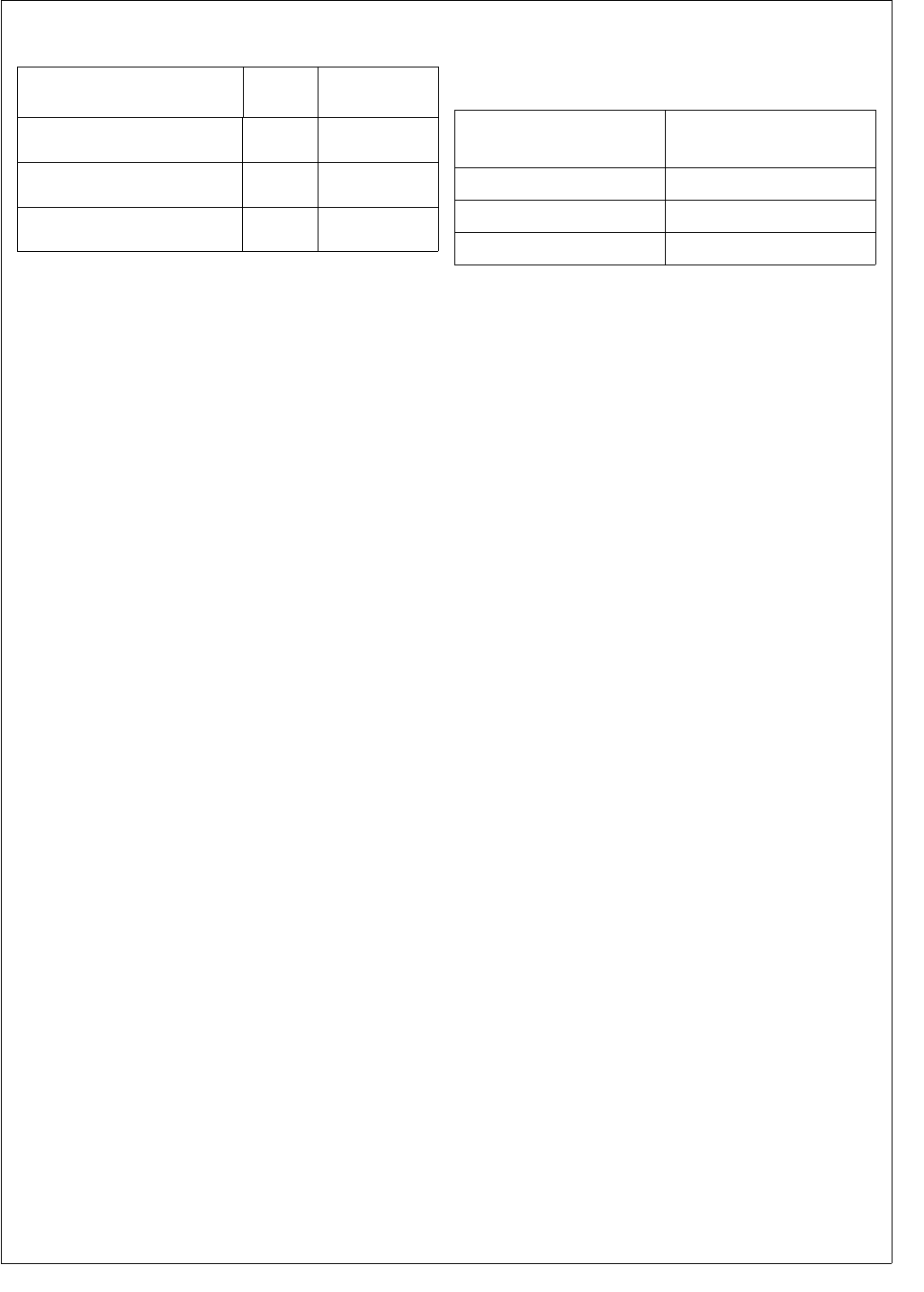

Table 65 CAN Module Internal Timing

Task

Cycle

Count

Occurrence/

Frame

Copy hidden buffer to receive

message buffer

17 0–1

Update status from TX_RTR

to TX_ONCE_RTR

30–15

Schedule a message for

transmission

2 0–1

Table 66 Minimum Clock Frequency Requirements

Baud Rate

Minimum Clock

Frequency

1 Mbit/sec 15.25 MHz

500 kbit/sec 7.625 MHz

250 kbit/sec 3.81 MHz