125 www.national.com

CP3BT26

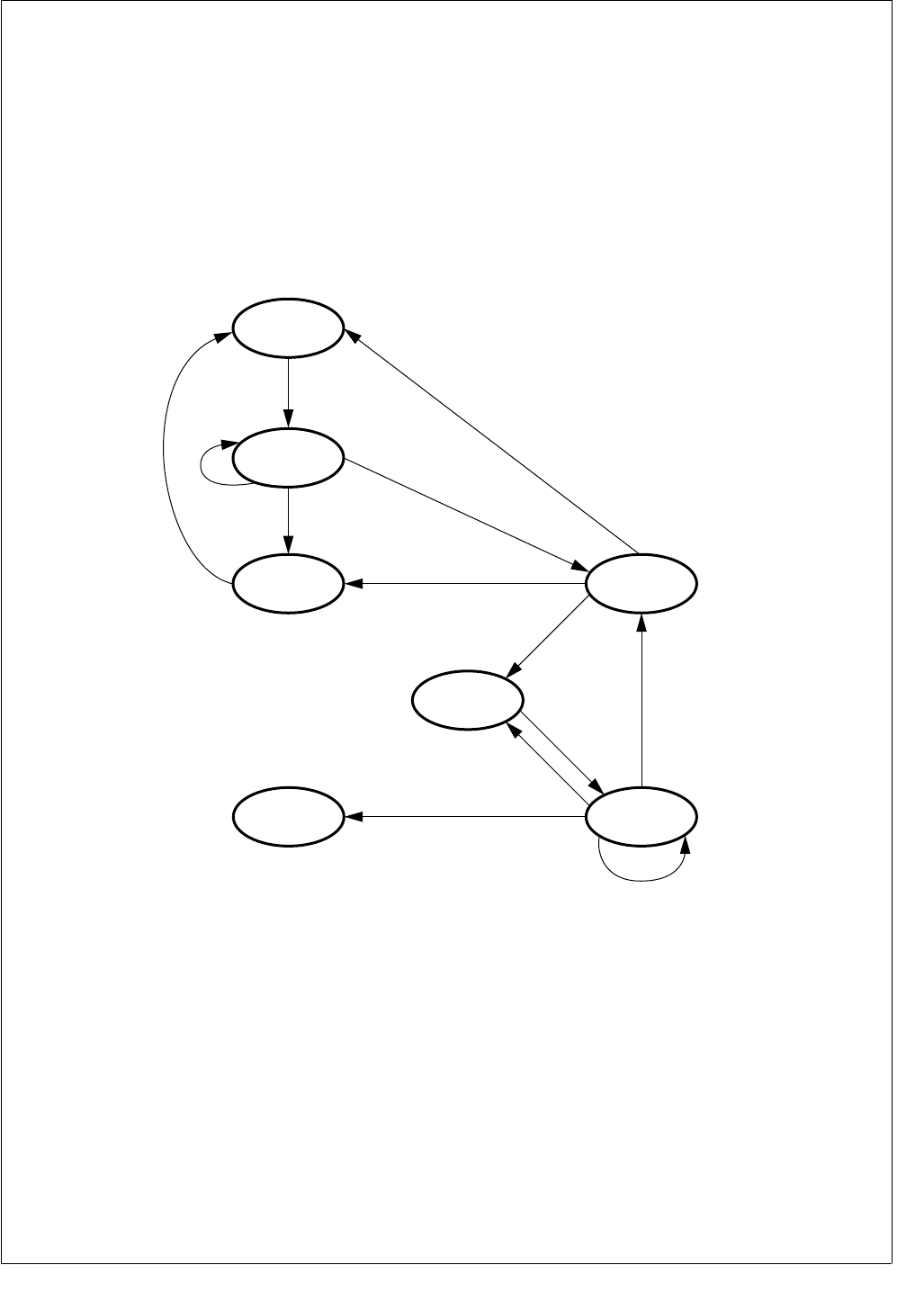

19.6.4 TX Buffer States

The transmission process can be started after software has

loaded the buffer registers (data, ID, DLC, PRI) and set the

buffer status from TX_NOT_ACTIVE to TX_ONCE,

TX_RTR, or TX_ONCE_RTR.

When the CPU writes TX_ONCE, the buffer will be

TX_BUSY as soon as the CAN module has scheduled this

buffer for the next transmission. After the frame could be

successfully transmitted, the buffer status will be automati-

cally reset to TX_NOT_ACTIVE when a data frame was

transmitted or to RX_READY when a remote frame was

transmitted.

If the CPU configures the message buffer to

TX_ONCE_RTR, it will transmit its data contents. During the

transmission, the buffer state is 1111b as the CPU wrote

1110b into the status section of the CNSTAT register. After

the successful transmission, the buffer enters the TX_RTR

state and waits for a remote frame. When it receives a re-

mote frame, it will go back into the TX_ONCE_RTR state,

transmit its data bytes, and return to TX_RTR. If the CPU

writes 1010b into the buffer status section, it will only enter

the TX_RTR state, but it will not send its data bytes before

it waits for a remote frame. Figure 58 illustrates the possible

transmit buffer states.

Figure 58. Transmit Buffer States

19.7 INTERRUPTS

The CAN module has one dedicated ICU interrupt vector for

all interrupt conditions. In addition, the data frame receive

event is an input to the MIWU (see Section 13.0). The inter-

rupt process can be initiated from the following sources.

CAN data transfer

— Reception of a valid data frame in the buffer. (Buffer

state changes from RX_READY to RX_FULL or

RX_OVERRUN.)

— Successful transmission of a data frame. (Buffer state

changes from TX_ONCE to TX_NOT_ACTIVE or

RX_READY.)

— Successful response to a remote frame. (Buffer state

changes from TX_ONCE_RTR to TX_RTR.)

— Transmit scheduling. (Buffer state changes from

TX_RTR to TX_ONCE_RTR.)

CAN error conditions

— Detection of an CAN error. (The CEIPND bit in the

CIPND register will be set as well as the correspond-

ing bits in the error diagnostic register CEDIAG.)

The receive/transmit interrupt access to every message

buffer can be individually enabled/disabled in the CIEN reg-

ister. The pending flags of the message buffer are located in

the CIPND register (read only) and can be cleared by reset-

ting the flags in the CICLR registers.

TX_ONCE_RTR

1110

CAN

schedules TX

RTR

received

TX done

Transmit

request cancelled

CPU writes 1000

Remote transmission

request sent - now wait

to receive a data frame

TX request delayed

by a TX request of higher

priority message

Transmit

request cancelled

CPU writes 1000

CAN

schedules TX

TX request

CPU writes 1100

TX request

CPU writes 1110

CPU writes 1010

TX_BUSY2

1111

TX done

transmit failed

TX_RTR

1010

TX_NOT_ACTIVE

1000

TX_BUSY0

1101

RX_READY

0010

TX_ONCE

1100

transmit failed

DS042