www.national.com 64

CP3BT26

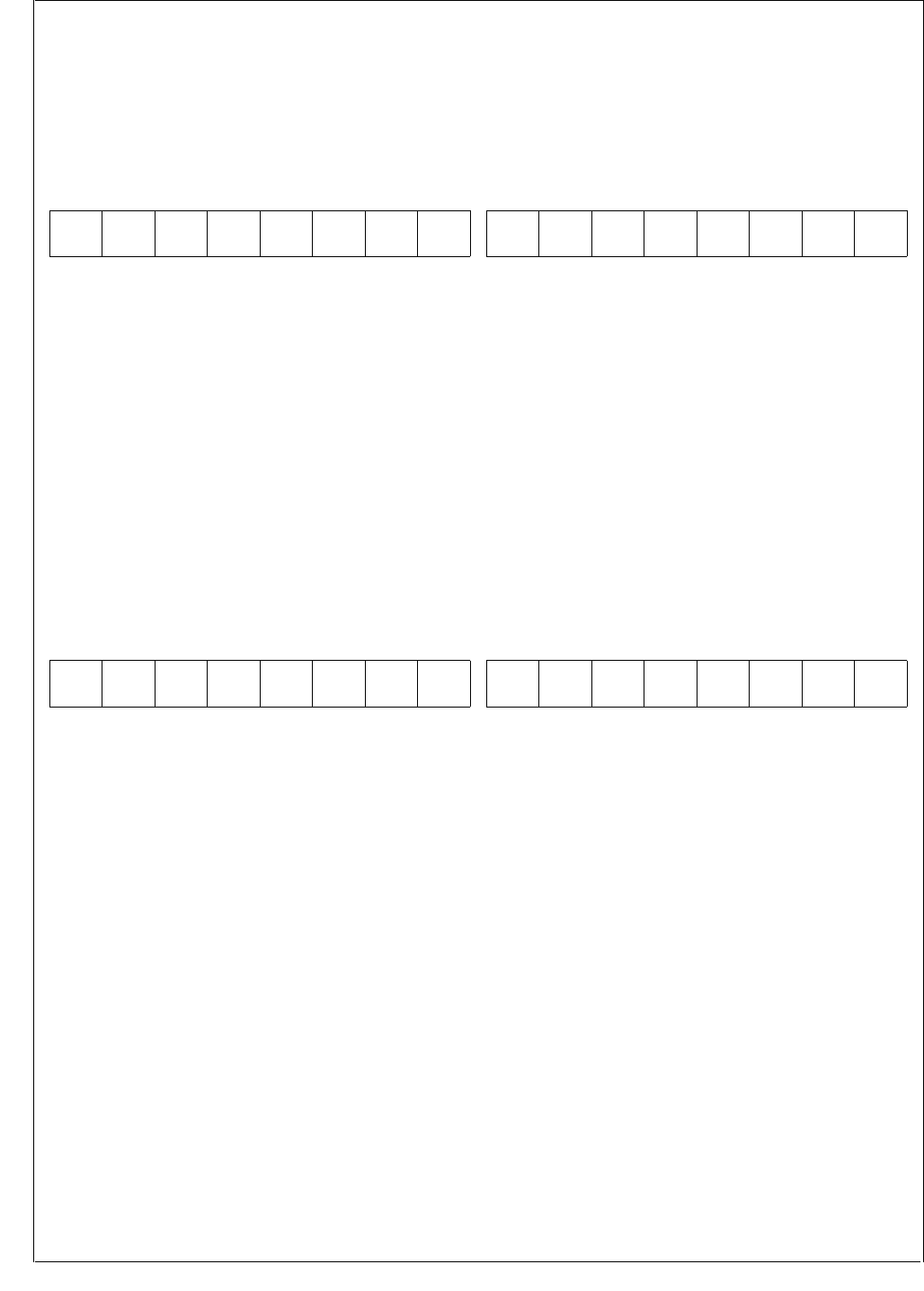

13.1.7 Wake-Up Interrupt Control Register 1

(WK0ICTL1)

The WK0ICTL1 register is a word-wide read/write register

that selects the interrupt request signal for the associated

MIWU channels WUI7:0. At reset, the WK0ICTL1 register is

cleared, which selects MIWU Interrupt Request 0 for all

eight channels. The register format is shown below.

WKINTR The Wake-Up Interrupt Request Select fields

select which of the four MIWU interrupt re-

quests are activated for the corresponding

channel.

00 – Selects MIWU interrupt request 0.

01 – Selects MIWU interrupt request 1.

10 – Selects MIWU interrupt request 2.

11 – Selects MIWU interrupt request 3.

13.1.8 Wake-Up 1 Interrupt Control Register 1

(WK1ICTL1)

The WK1ICTL1 register is a word-wide read/write register

that selects the interrupt request signal for the associated

MIWU channels WUI23:16. At reset, the WK1ICTL1 register

is cleared, which selects MIWU Interrupt Request 4 for all

eight channels. The register format is shown below.

WKINTR The Wake-Up Interrupt Request Select fields

select which of the four MIWU interrupt re-

quests are activated for the corresponding

channel.

00 – Selects MIWU interrupt request 4.

01 – Selects MIWU interrupt request 5.

10 – Selects MIWU interrupt request 6.

11 – Selects MIWU interrupt request 7.

13.1.9 Wake-Up Interrupt Control Register 2

(WK0ICTL2)

The WK0ICTL2 register is a word-wide read/write register

that selects the interrupt request signal for the associated

MIWU channels WUI15:8. At reset, the WK2ICTL2 register

is cleared, which selects MIWU Interrupt Request 0 for all

eight channels. The register format is shown below.

WKINTR The Wake-Up Interrupt Request Select fields

select which of the four MIWU interrupt re-

quests are activated for the corresponding

channel.

00 – Selects MIWU interrupt request 0.

01 – Selects MIWU interrupt request 1.

10 – Selects MIWU interrupt request 2.

11 – Selects MIWU interrupt request 3.

13.1.10 Wake-Up 1 Interrupt Control Register 2

(WK1ICTL2)

The WK1ICTL2 register is a word-wide read/write register

that selects the interrupt request signal for the associated

MIWU channels WUI31:24. At reset, the WK1ICTL2 register

is cleared, which selects MIWU Interrupt Request 4 for all

eight channels. The register format is shown below.

WKINTR The Wake-Up Interrupt Request Select fields

select which of the four MIWU interrupt re-

quests are activated for the corresponding

channel.

00 – Selects MIWU interrupt request 4.

01 – Selects MIWU interrupt request 5.

10 – Selects MIWU interrupt request 6.

11 – Selects MIWU interrupt request 7.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

WKIN

TR7

WKIN

TR6

WKIN

TR5

WKIN

TR4

WKIN

TR3

WKIN

TR2

WKIN

TR1

WKIN

TR0

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

WKIN

TR23

WKIN

TR22

WKIN

TR21

WKIN

TR20

WKIN

TR19

WKIN

TR18

WKIN

TR17

WKIN

TR16

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

WKIN

TR15

WKIN

TR14

WKIN

TR13

WKIN

TR12

WKIN

TR11

WKIN

TR10

WKIN

TR9

WKIN

TR8

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

WKIN

TR31

WKIN

TR30

WKIN

TR29

WKIN

TR28

WKIN

TR27

WKIN

TR26

WKIN

TR25

WKIN

TR24