151 www.national.com

CP3BT26

20.6.6 Freeze Mode

The audio interface provides a FREEZE input, which allows

to freeze the status of the audio interface while a develop-

ment system examines the contents of the FIFOs and reg-

isters.

When the FREEZE input is asserted, the audio interface be-

haves as follows:

The receive FIFO or receive DMA registers are not up-

dated with new data.

The receive status bits (RXO, RXE, RXF, and RXAF) are

not changed, even though the receive FIFO or receive

DMA registers are read.

The transmit shift register (ATSR) is not updated with

new data from the transmit FIFO or transmit DMA regis-

ters.

The transmit status bits (TXU, TXF, TXE, and TXAE) are

not changed, even though the transmit FIFO or transmit

DMA registers are written.

The time at which these registers are frozen will vary be-

cause they operate from a different clock than the one used

to generate the freeze signal.

20.7 AUDIO INTERFACE REGISTERS

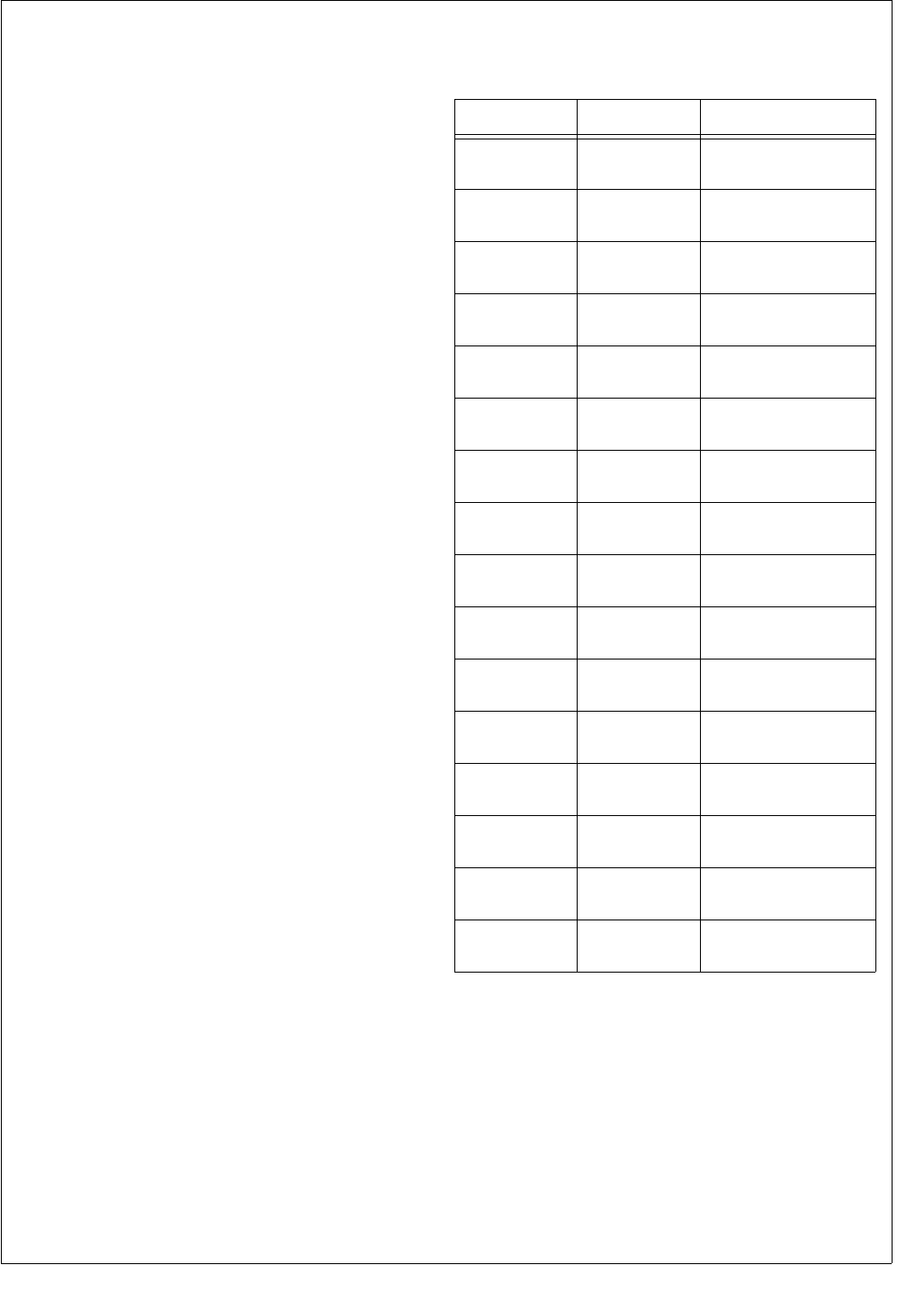

Table 67 Audio Interface Registers

Name Address Description

ARFR FF FD40h

Audio Receive FIFO

Register

ARDR0 FF FD42h

Audio Receive DMA

Register 0

ARDR1 FF FD44h

Audio Receive DMA

Register 1

ARDR2 FF FD46h

Audio Receive DMA

Register 2

ARDR3 FF FD48h

Audio Receive DMA

Register 3

ATFR FF FD4Ah

Audio Transmit FIFO

Register

ATDR0 FF FD4Ch

Audio Transmit DMA

Register 0

ATDR1 FF FD4Eh

Audio Transmit DMA

Register 1

ATDR2 FF FD50h

Audio Transmit DMA

Register 2

ATDR3 FF FD52h

Audio Transmit DMA

Register 3

AGCR FF FD54h

Audio Global

Configuration Register

AISCR FF FD56h

Audio Interrupt Status

and Control Register

ARSCR FF FD58h

Audio Receive Status

and Control Register

ATSCR FF FD5Ah

Audio Transmit Status

and Control Register

ACCR FF FD5Ch

Audio Clock Control

Register

ADMACR FF FD5Eh

Audio DMA Control

Register