www.national.com 172

CP3BT26

22.3.10 UART Mode Select Register 2 (UnMDSL2)

The UnMDSL2 register is a byte-wide, read/write register

that controls the sample mode used to recover asynchro-

nous data. At reset, the UnOVR register is cleared. The reg-

ister format is shown below.

USMD The USMD bit controls the sample mode for

asynchronous transmission.

0 – UART determines the sample position au-

tomatically.

1 – The UnSPOS register determines the

sample position.

22.3.11 UART Sample Position Register (UnSPOS)

The UnSPOS register is a byte-wide, read/write register that

specifies the sample position when the USMD bit in the

UnMDSL2 register is set. At reset, the UnSPOS register is

initialized to 06h. The register format is shown below.

USAMP The Sample Position field specifies the over-

sample clock period at which to take the first

of three samples for sensing the value of data

bits. The clocks are numbered starting at 0

and may range up to 15 for 16× oversampling.

The maximum value for this field is (oversam-

pling rate - 3). The table below shows the

clock period at which each of the three sam-

ples is taken, when automatic sampling is en-

abled (UnMDSL2.USMD = 0).

The USAMP field may be used to override the

automatic selection, to choose any other clock

period at which to start taking the three sam-

ples.

22.4 BAUD RATE CALCULATIONS

The UART baud rate is determined by the System Clock fre-

quency and the values in the UnOVR, UnPSR, and Un-

BAUD registers. Unless the System Clock is an exact

multiple of the baud rate, there will be a small amount of er-

ror in the resulting baud rate.

22.4.1 Asynchronous Mode

The equation to calculate the baud rate in asynchronous

mode is:

where BR is the baud rate, SYS_CLK is the System Clock,

O is the oversample rate, N is the baud rate divisor + 1, and

P is the prescaler divisor selected by the UPSR register.

Assuming a System Clock of 5 MHz, a desired baud rate of

9600, and an oversample rate of 16, the N × P term accord-

ing to the equation above is:

The N × P term is then divided by each Prescaler Factor

from Table 69 to obtain a value closest to an integer. The

factor for this example is 6.5.

The baud rate register is programmed with a baud rate divi-

sor of 4 (N = baud rate divisor + 1). This produces a baud

clock of:

Note that the percent error is much lower than would be pos-

sible without the non-integer prescaler factor. Error greater

than 3% is marginal and may result in unreliable operation.

Refer to Table 71 below for more examples.

7 1 0

Reserved USMD

7 4 3 0

Reserved USAMP

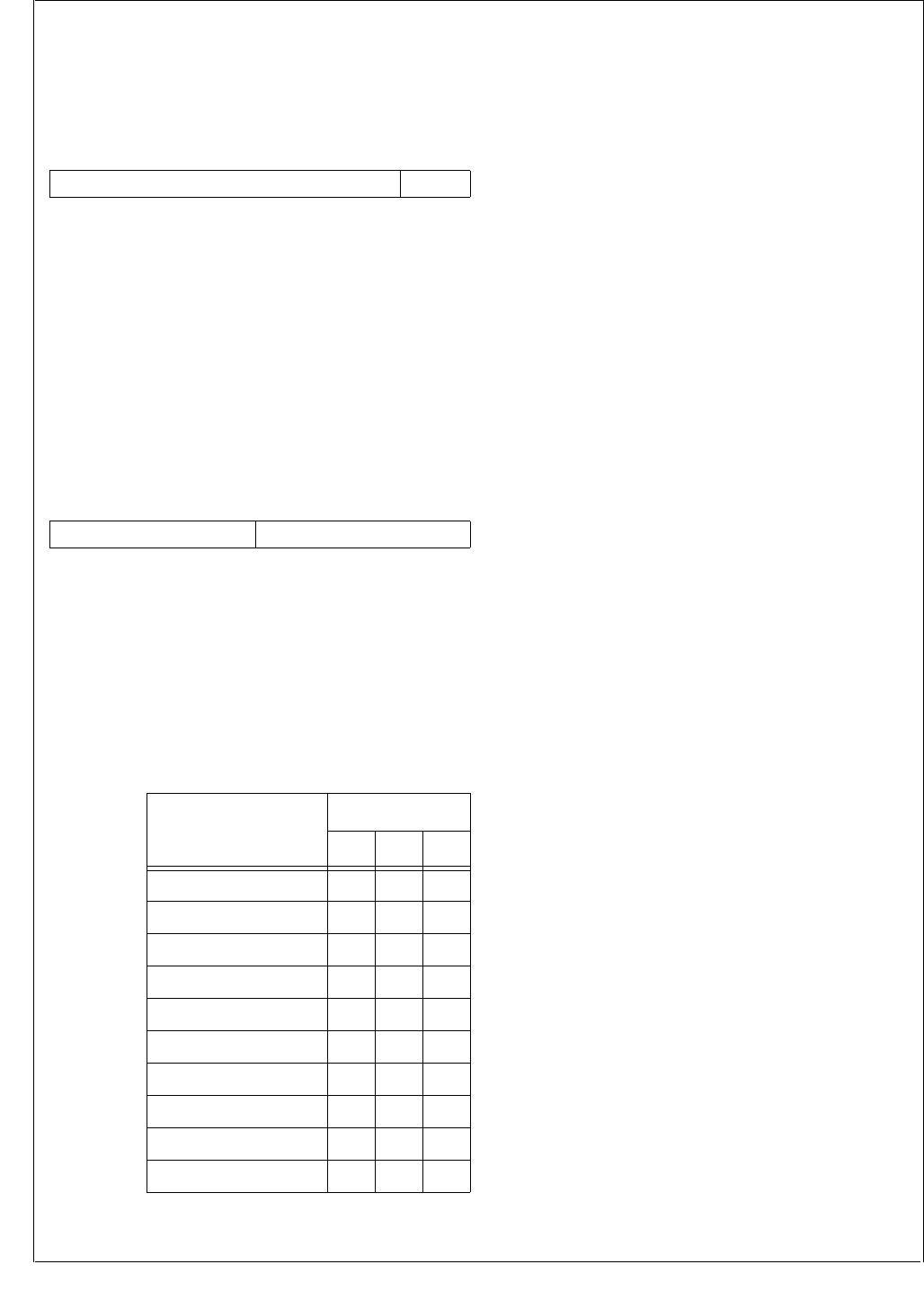

Oversampling Rate

Sample Position

123

7 234

8 234

9 345

10 345

11 456

12 456

13 567

14 567

15 678

16 678

BR

SYS_CLK

O NP××()

------------------------------=

NP×

5

6

×10()

16 9600×()

------------------------------- 32.552==

N

32.552

6.5

------------------ 5.008 (N = 5)==

BR

5

6

×10()

16 5 6.5××()

----------------------------------- 9615.385==

%error

9615.385 9600–()

9600

------------------------------------------------- 0.16==