167 www.national.com

CP3BT26

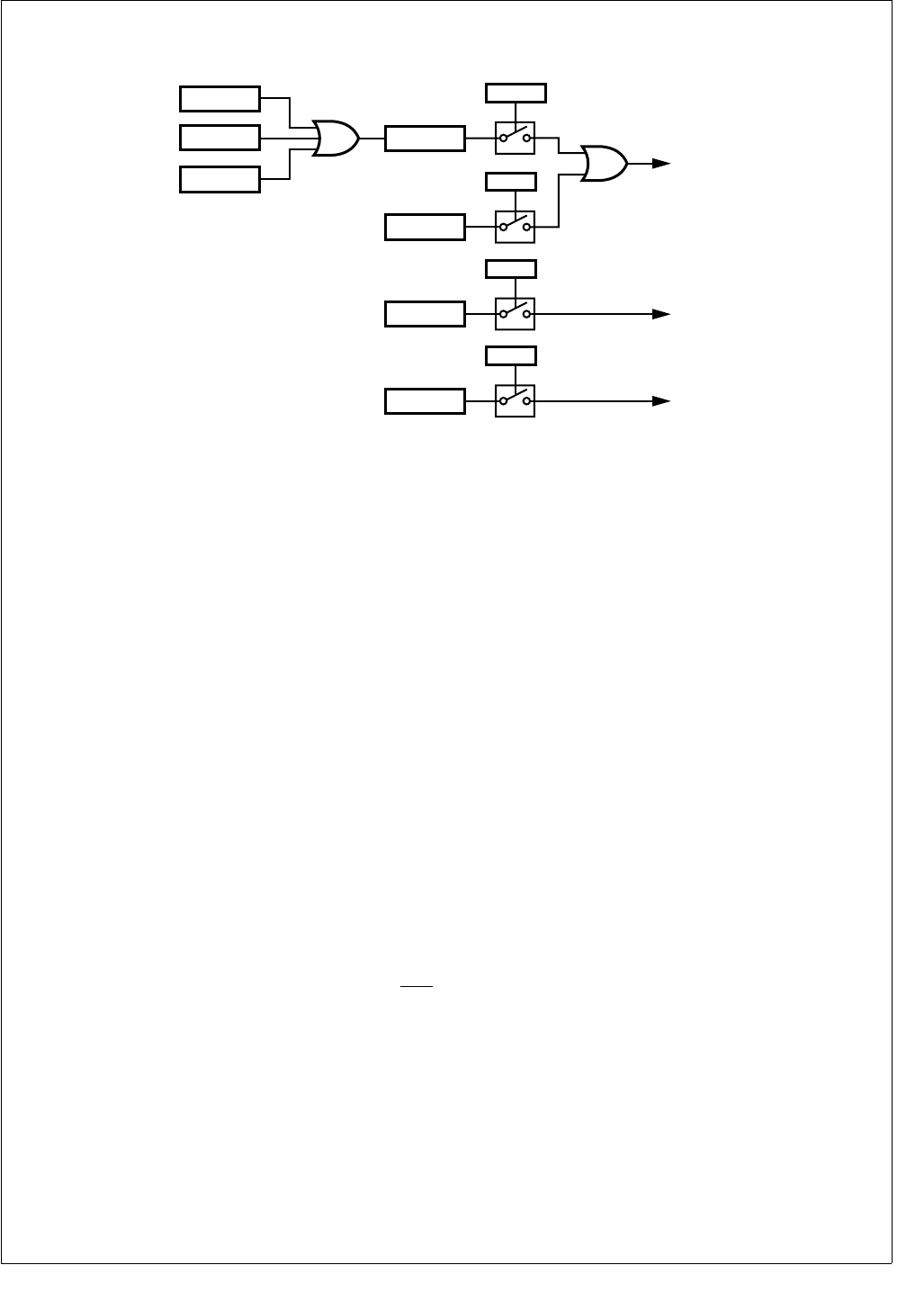

Figure 82 shows a diagram of the interrupt sources and as-

sociated enable bits.

Figure 82. UART Interrupts

The interrupts can be individually enabled or disabled using

the Enable Transmit Interrupt (UETI), Enable Receive Inter-

rupt (UERI), and Enable Receive Error Interrupt (UEER)

bits in the UnICTRL register.

A transmit interrupt is generated when both the UTBE and

UETI bits are set. To remove this interrupt, software must ei-

ther disable the interrupt by clearing the UETI bit or write to

the UnTBUF register (which clears the UTBE bit).

A receive interrupt is generated on these conditions:

Both the URBF and UERI bits are set. To remove this in-

terrupt, software must either disable the interrupt by

clearing the UERI bit or read from the URBUF register

(which clears the URBF bit).

Both the UERR and the UEEI bits are set. To remove this

interrupt, software must either disable the interrupt by

clearing the UEEI bit or read the UnSTAT register (which

clears the UERR bit).

A flow control interrupt is generated when both the UDCTS

and the UEFCI bits are set. To remove this interrupt, soft-

ware must either disable the interrupt by clearing the UEFCI

bit or reading the UnICTRL register (which clears the

UDCTS bit).

In addition to the dedicated inputs to the ICU for UART in-

terrupts, the UART receive (RXD) and Clear To Send (CTS

)

signals are inputs to the MIWU (see Section 13.0), which

can be programmed to generate edge-triggered interrupts.

22.2.8 DMA Support

The UART module can operate with one or two DMA chan-

nels. Two DMA channels must be used for processor-inde-

pendent full-duplex operation. Both receive and transmit

DMA can be enabled simultaneously.

If transmit DMA is enabled (the UETD bit is set), the UART

generates a DMA request when the UTBE bit changes state

from clear to set. Enabling transmit DMA automatically dis-

ables transmit interrupts, without regard to the state of the

UETI bit.

If receive DMA is enabled (the UERD bit is set), the UART

generates a DMA request when the URBF bit changes state

from clear to set. Enabling receive DMA automatically dis-

ables receive interrupts, without regard to the state of the

UERI bit. However, receive error interrupts should be en-

abled (the UEEI bit is set) to allow detection of receive errors

when DMA is used.

22.2.9 Break Generation and Detection

A line break is generated when the UBRK bit is set in the

UnMDSL1 register. The TXD line remains low until the pro-

gram resets the UBRK bit.

A line break is detected if RXD remains low for 10 bit times

or longer after a missing stop bit is detected.

22.2.10 Parity Generation and Detection

Parity is only generated or checked with the 7-bit and 8-bit

data formats. It is not generated or checked in the diagnostic

loopback mode, the attention mode, or in normal mode with

the 9-bit data format. Parity generation and checking are en-

abled and disabled using the PEN bit in the UnFRS register.

The UPSEL bits in the UnFRS register are used to select

odd, even, or no parity.

RX

Interrupt

UERR

UEEI

TX

Interrupt

UTBE

UETI

URBF

UFE

UDOE

UPE

UERI

FC

Interrupt

UDCTS

UEFCI

DS066