www.national.com 156

CP3BT26

20.7.8 Audio Transmit Status and Control Register

(ATSCR)

The ASCR register controls the basic operation of the inter-

face. It also holds bits which report the current status of the

audio communication. The CPU bus master has read/write

access to the ASCR register. At reset, this register is loaded

with F003h.

TXAE The Transmit FIFO Almost Empty bit is set

when the number of data bytes/words in

transmit buffer is equal to the specified warn-

ing limit.

0 – Transmit FIFO above warning limit.

1 – Transmit FIFO at or below warning limit.

TXE The Transmit FIFO Empty bit is set when the

transmit buffer is empty. The TXE bit is set to

one every time the TRP is equal to the TWP

and the last access to the FIFO was read op-

eration (into ATSR).

0 – Transmit FIFO not empty.

1 – Transmit FIFO empty.

TXF The Transmit FIFO Full bit is set when the

TWP is equal to the TRP and the last access

to the FIFO was write operation (write to AT-

DR).

0 – Transmit FIFO not full.

1 – Transmit FIFO full.

TXU The Transmit Underflow bit indicates that the

transmit shift register (ATSR) has underrun.

This occurs when the transmit FIFO was al-

ready empty and a complete data word has

been transferred. In this case, the TRP will be

decremented by 1 and the previous data will

be retransmitted. No transmit interrupt and no

DMA request will be generated (even if en-

abled).

0 – Transmit underrun occurred.

1 – Transmit underrun did not occur.

TXSA The Transmit Slot Assignment field specifies

during which slots the transmitter is active and

drives data through the STD pin. The STD pin

is in high impedance state during all other

slots. If the frame consists of less than 4 slots,

the TXSA bits for unused slots are ignored.

For example, if a frame only consists of 2

slots, TXSA bits 2 and 3 are ignored. The fol-

lowing table shows the slot assignment

scheme.

After reset, the TXSA field is clear, so soft-

ware must load the correct slot assignment.

TXDSA The Transmit DMA Slot Assignment field

specifies which slots (audio channels) are

supported by DMA. If the TXDSA bit is set for

an assigned slot n (TXSAn = 1), the data to be

transmitted within this slot will not be read

from the transmit FIFO, but will instead be

read from the corresponding Transmit DMA

data register (ATDRn). A DMA request n is as-

serted when the ATDRn is empty. If the TSA

bit for a slot is clear, the TXDSA bit is ignored.

The following table shows the DMA slot as-

signment scheme.

TFWL The Transmit FIFO Warning Level field speci-

fies when a transmit interrupt is asserted. A

transmit interrupt is asserted when the num-

ber of bytes or words in the transmit FIFO is

equal or less than the warning level value. A

TXFWL value of Fh means that a transmit in-

terrupt is asserted if one or more bytes or

words are available in the transmit FIFO. At

reset, the TXFWL field is loaded with Fh.

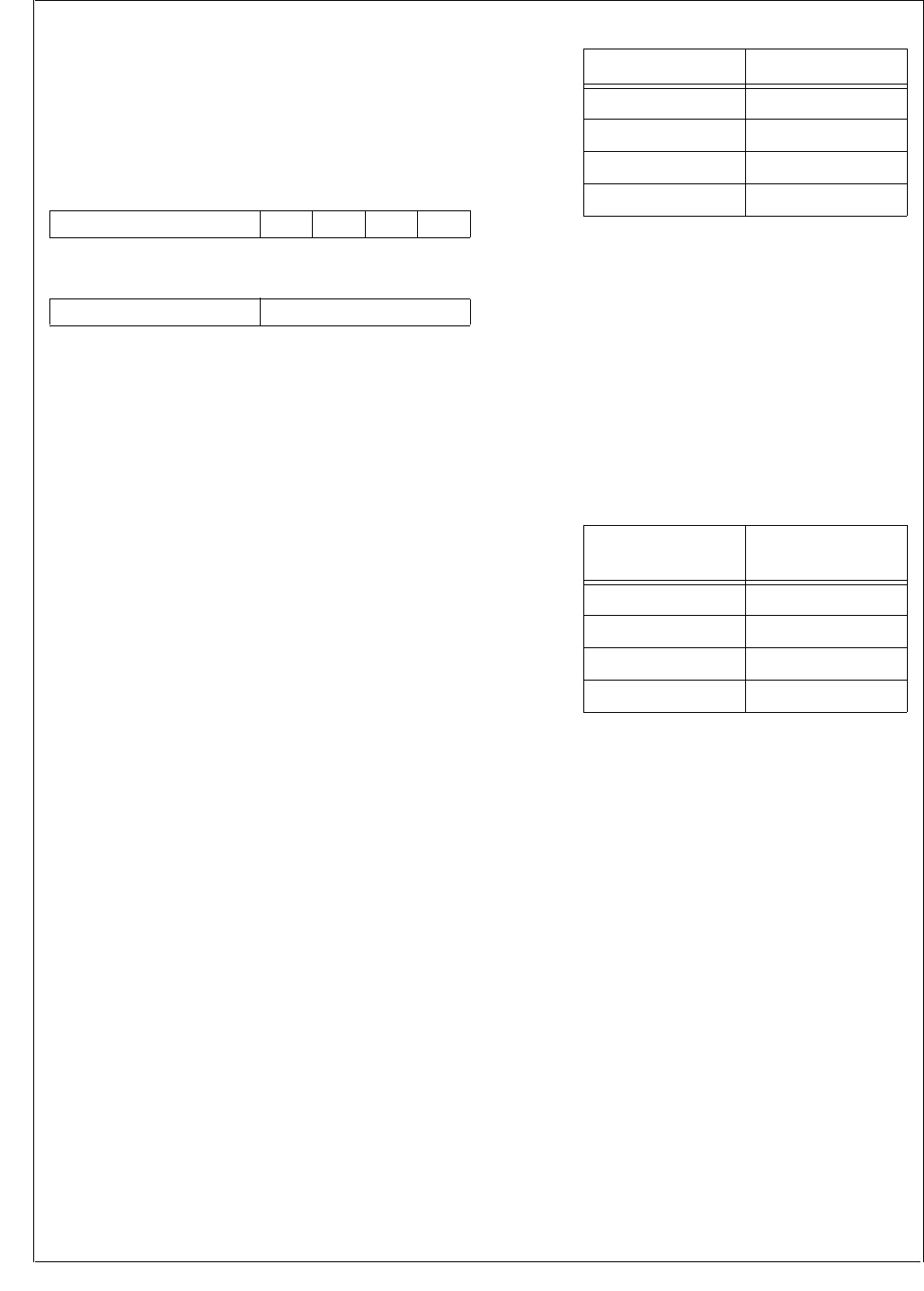

7 4 3 2 1 0

TXSA TXU TXF TXE TXAE

15 12 11 8

TXFWL TXDSA

TXSA Bit Slots Enabled

TXSA0 0

TXSA1 1

TXSA2 2

TXSA3 3

TXDSA Bit

Slots Enabled

for DMA

TXDSA0 0

TXDSA1 1

TXDSA2 2

TXDSA3 3