61 www.national.com

CP3BT26

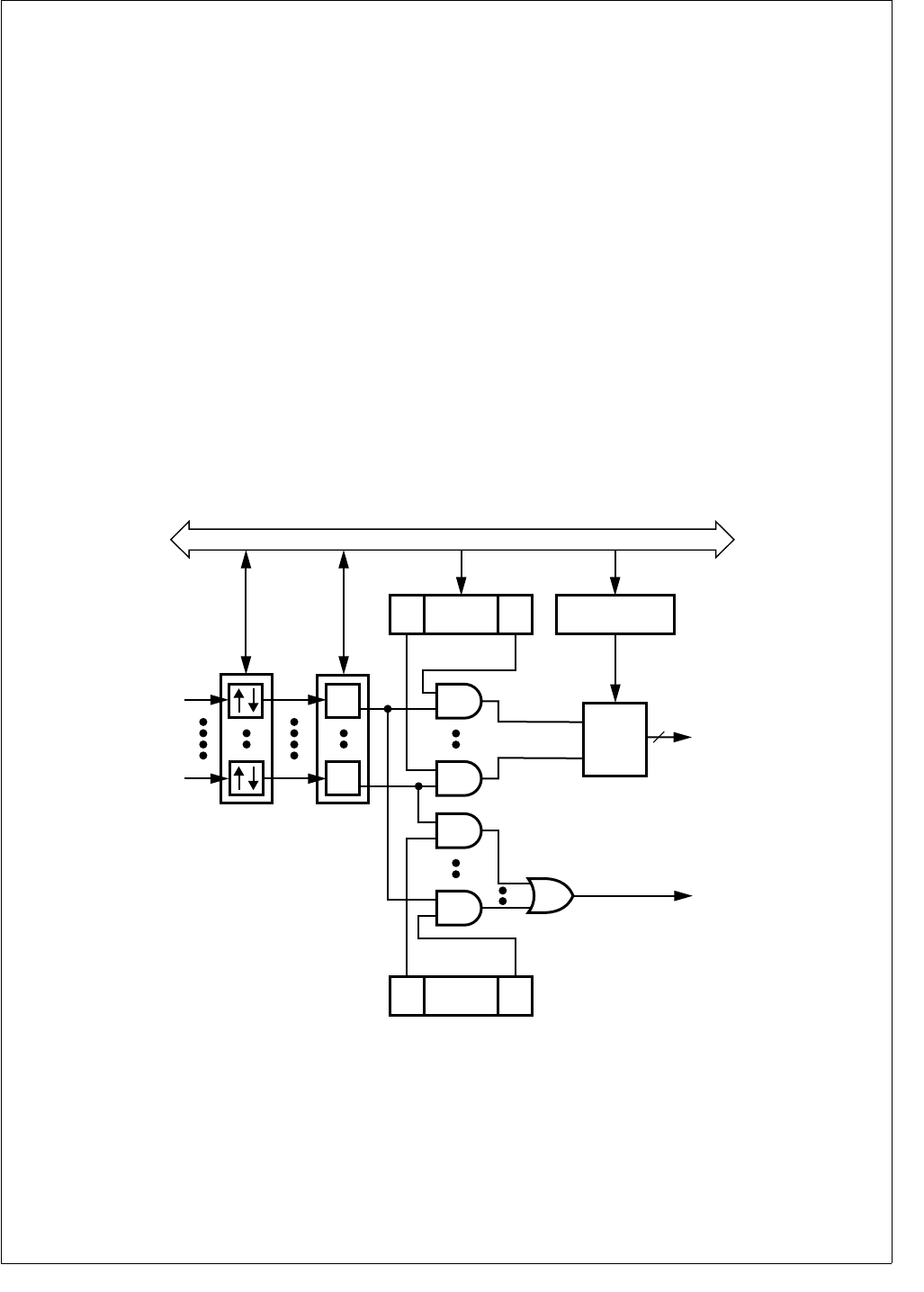

13.0 Multi-Input Wake-Up

The Multi-Input Wake-Up (MIWU) unit consists of two iden-

tical 16-channel modules. Each module can assert a wake-

up signal for exiting from a low-power mode, and each can

assert an interrupt request on any of four Interrupt Control

Unit (ICU) channels assigned to that module. The modules

operate independently, so each may assert an interrupt re-

quest to the ICU. Together, these modules provide 32 MIWU

input channels and 8 interrupt request outputs.

Each 16-channel module monitors its inputs for a software-

selectable trigger condition. On detection of a trigger condi-

tion, the module generates an interrupt request and if en-

abled, a wake-up request. A wake-up request can be used

by the power management unit to exit the Halt, Idle, or Pow-

er Save mode and return to the Active mode. An interrupt

request generates an interrupt to the CPU, which allows an

interrupt handler to respond to MIWU events.

The wake-up event only activates the clocks and CPU, but

does not by itself initiate execution of any code. It is the in-

terrupt request asserted by the MIWU that gets the CPU to

start executing code, by jumping to the corresponding inter-

rupt handler. Therefore, setting up the MIWU interrupt han-

dler is essential for any wake-up operation.

Each 16-channel module has four interrupt requests that

can be routed to the ICU as shown in Figure 9. Each of the

16 channels can be programmed to activate one of these

four interrupt requests.

The 32 MIWU channels are named WUI0 through WUI31,

as shown in Table 27.

Each channel can be configured to trigger on rising or falling

edges, as determined by the setting in the WK0EDG or

WK1EDG register. Each trigger event is latched into the

WK0PND or WK1PND register. If a trigger event is enabled

by its respective bit in the WK0ENA or WK1ENA register, an

active wake-up/interrupt signal is generated. Software can

determine which channel has generated the active signal by

reading the WK0PND or WK1PND register.

The MIWU is active at all times, including the Halt mode. All

device clocks are stopped in this mode. Therefore, detecting

an external trigger condition and the subsequent setting of

the pending bit are not synchronous to the System Clock.

Figure 9. Multi-Input Wake-Up Module Block Diagram

WK0EDG

WK1EDG

WK0PND

WK1PND

WUI16

WUI31

Wake-Up Signal

To Power Mgt

0

15

Peripheral Bus

WK0ICTL1/WK0ICTL2

WK1ICTL1/WK1ICTL2

15

. . . . . . . . . . .

WK0IENA

WK1IENA

0

15

. . . . . . . . . . .

WK0ENA

WK1ENA

0

MIWU Interrupt 3:0

MIWU Interrupt 7:4

Encoder

4

DS218

WUI0

WUI15