45 www.national.com

CP3BT26

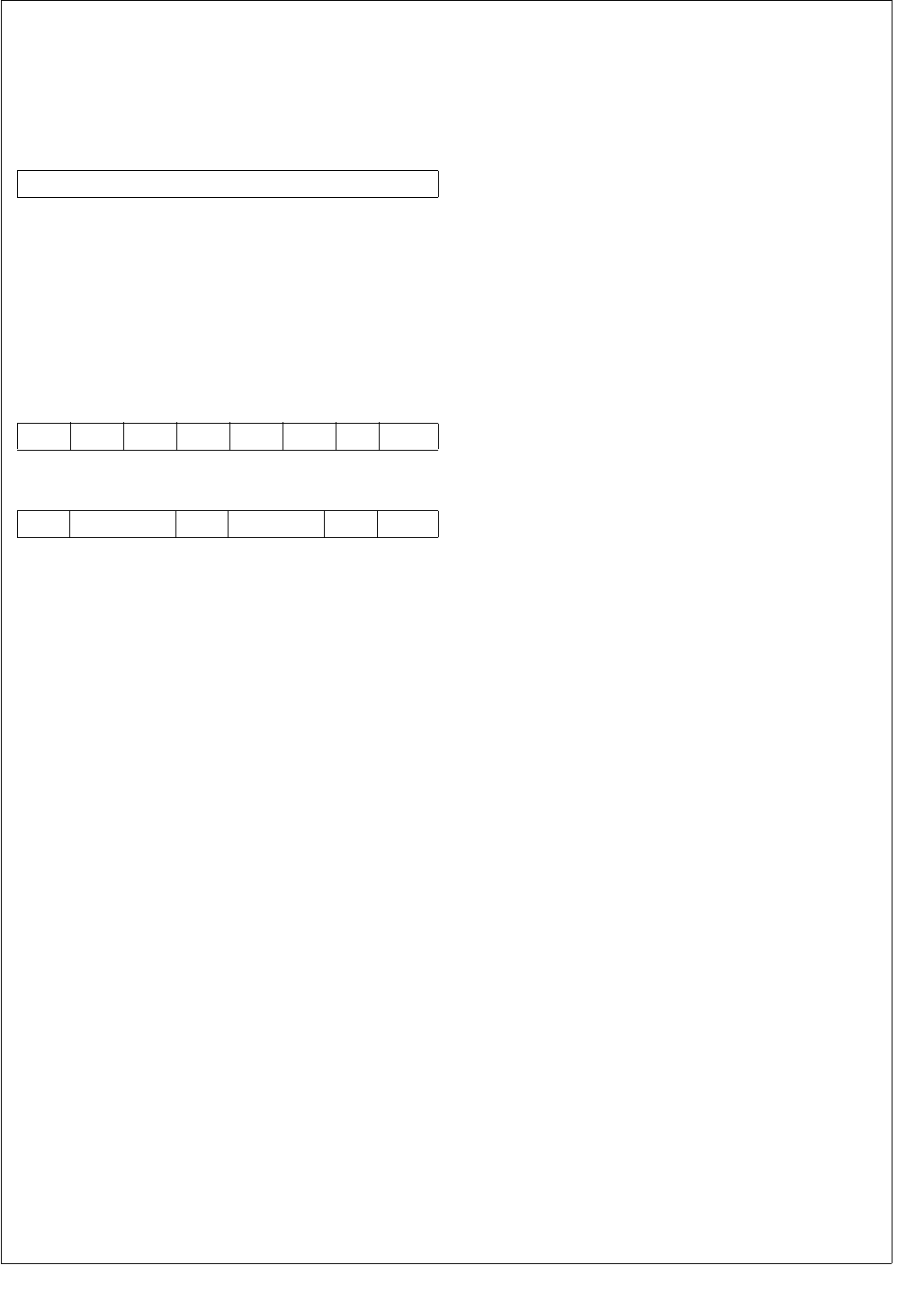

9.6.6 Block Length Register (BLTRn)

The Block Length register is a 16-bit, read/write register. It

holds the number of DMA transfers to be performed for the

next block. Writing this register automatically sets the DM-

ASTAT.VLD bit.

Note: 0000h is interpreted as 2

16

-1 transfer cycles.

9.6.7 DMA Control Register (DMACNTLn)

The DMA Control register n is a word-wide, read/write reg-

ister that controls the operation of DMA channel n. This reg-

ister is cleared at reset. Reserved bits must be written with

0.

CHEN The Channel Enable bit must be set to enable

any DMA operation on this channel. Writing a

1 to this bit starts a new DMA transfer even if

it is currently a 1. If all DMACNTLn.CHEN bits

are clear, the DMA clock is disabled to reduce

power.

0

– Channel disabled.

1 – Channel enabled.

ETC If the Enable Interrupt on Terminal Count bit is

set, it enables an interrupt when the DMAS-

TAT.TC bit is set.

0

– Interrupt disabled.

1

– Interrupt enabled.

EOVR If the Enable Interrupt on OVR bit is set, it en-

ables an interrupt when the DMASTAT.OVR

bit is set.

0

– Interrupt disabled.

1

– Interrupt enabled.

TCS The Transfer Cycle Size bit specifies the num-

ber of bytes transferred in each DMA transfer

cycle. In direct (fly-by) mode, undefined re-

sults occur if the TCS bit is not equal to the ad-

dressed memory bus width.

0

– Byte transfers (8 bits per cycle).

1

– Word transfers (16 bits per cycle).

IND The Direct/Indirect Transfer bit specifies the

transfer type.

0

– Direct transfer (flyby).

1

– Indirect transfer (memory-to-memory).

DIR The Transfer Direction bit specifies the direc-

tion of the transfer relative to Device A.

0

– Device A (pointed to by the ADCAn regis-

ter) is the source. In Fly-By mode a read

transaction is initialized.

1

– Device A (pointed to by the ADCAn regis-

ter) is the destination. In Fly-By mode a

write transaction is initialized.

OT The Operation Type bit specifies the operation

mode of the DMA controller.

0

– Single-buffer mode or double-buffer mode

enabled.

1

– Auto-Initialize mode enabled.

BPC The Bus Policy Control bit specifies the bus

policy applied by the DMA controller. The op-

eration mode can be either intermittent (cycle

stealing) or continuous (burst).

0

– Intermittent operation. The DMAC chan-

nel relinquishes the bus after each trans-

action, even if the request is still asserted.

1

– Continuous operation. The DMAC chan-

nel n uses the bus continuously as long

as the request is asserted. This mode can

only be used for software DMA requests.

For hardware DMA requests, the BPC bit

must be clear.

SWRQ The Software DMA Request bit is written with

a 1 to initiate a software DMA request. Writing

a 0 to this bit deactivates the software DMA

request. The SWRQ bit must only be written

when the DMRQ signal for this channel is in-

active (DMASTAT.CHAC = 0).

0

– Software DMA request is inactive.

1 – Software DMA request is active.

ADA If the Device A Address Control bit is set, it en-

ables updating the Device A address.

0 – ADCAn address unchanged.

1 – ADCAn address incremented or decre-

mented, according to INCA field of

DMACNTLn register.

INCA The Increment/Decrement ADCAn field spec-

ifies the step size for the Device A address in-

crement/decrement.

00 – Increment ADCAn register by 1.

01 – Increment ADCAn register by 2.

10 – Decrement ADCAn register by 1.

11 – Decrement ADCAn register by 2.

ADB If the Device B Address Control bit is set, it en-

ables updating the Device B Address.

0

– ADCBn address unchanged.

1

– ADCBn address incremented or decre-

mented, according to INCB field of

DMACNTLn register.

INCB The Increment/Decrement ADCBn field spec-

ifies the step size for the Device B address in-

crement/decrement.

00 – Increment ADCBn register by 1.

01 – Increment ADCBn register by 2.

10 – Decrement ADCBn register by 1.

11 – Decrement ADCBn register by 2.

15 0

Block Length

76543210

BPC OT DIR IND TCS EOVR ETC CHEN

15 14 13 12 11 10 9 8

Res. INCB ADB INCA ADA SWRQ