47 www.national.com

CP3BT26

10.0 Interrupts

The Interrupt Control Unit (ICU) receives interrupt requests

from internal and external sources and generates interrupts

to the CPU. Interrupts from the timers, UARTs, Microwire/

SPI interface, and Multi-Input Wake-Up module are all

maskable interrupts. The highest-priority interrupt is the

Non-Maskable Interrupt (NMI), which is triggered by a falling

edge received on the NMI

input pin.

The priorities of the maskable interrupts are hardwired and

therefore fixed. The implemented interrupts are named

IRQ0 through IRQ47, in which IRQ0 has the lowest priority

and IRQ47 has the highest priority. (IRQ0 is not implement-

ed, so IRQ1 is the lowest priority interrupt that normally may

occur.)

10.1 NON-MASKABLE INTERRUPTS

The Interrupt Control Unit (ICU) receives the external NMI

input and generates the NMI signal driven to the CPU. The

NMI input is an asynchronous input with Schmitt trigger

characteristics and an internal synchronization circuit,

therefore no external synchronizing circuit is needed. The

NMI

pin triggers an exception on its falling edge.

10.1.1 Non-Maskable Interrupt Processing

The CPU performs an interrupt acknowledge bus cycle

when beginning to process a non-maskable interrupt.

At reset, NMI interrupts are disabled and must remain dis-

abled until software initializes the interrupt table, interrupt

base register (INTBASE), and the interrupt mode. The ex-

ternal NMI

interrupt is enabled by setting the EXNMI.EN-

LCK bit and will remain enabled until a reset occurs.

Alternatively, the external NMI interrupt can be enabled by

setting the EXNMI.EN bit and will remain enabled until an in-

terrupt event or a reset occurs.

10.2 MASKABLE INTERRUPTS

The ICU receives level-triggered interrupt request signals

from 47 sources and generates a vectored interrupt to the

CPU when required. Priority among the implemented inter-

rupt sources (named IRQ1 through IRQ47) is fixed.

The maskable interrupts are globally enabled and disabled

by the E bit in the PSR register. The EI and DI instructions

are used to set (enable) and clear (disable) this bit. The glo-

bal maskable interrupt enable bit (I bit in the PSR) must also

be set before any maskable interrupts are taken.

Each interrupt source can be individually enabled or dis-

abled under software control through the ICU interrupt en-

able registers and also through interrupt enable bits in the

peripherals that request the interrupts. The ICU supports

IRQ0, but in the CP3BT26 it is not connected to any inter-

rupt source.

10.2.1 Maskable Interrupt Processing

Interrupt vector numbers are always positive, in the range

10h to 3Fh. The IVCT register contains the interrupt vector

of the enabled and pending interrupt with the highest priori-

ty. The interrupt vector 10h corresponds to IRQ0 and the

lowest priority, while the vector 3Fh corresponds to IRQ47

and the highest priority. The CPU performs an interrupt ac-

knowledge bus cycle on receiving a maskable interrupt re-

quest from the ICU. During the interrupt acknowledge cycle,

a byte is read from address FF FE00h (IVCT register). The

byte is used as an index into the Dispatch Table to deter-

mine the address of the interrupt handler.

Because IRQ0 is not connected to any interrupt source, it

would seem that the interrupt vector would never return the

value 10h. If it does return a value of 10h, the entry in the

dispatch table should point to a default interrupt handler that

handles this error condition. One possible condition for this

to occur is deassertion of the interrupt before the interrupt

acknowledge cycle.

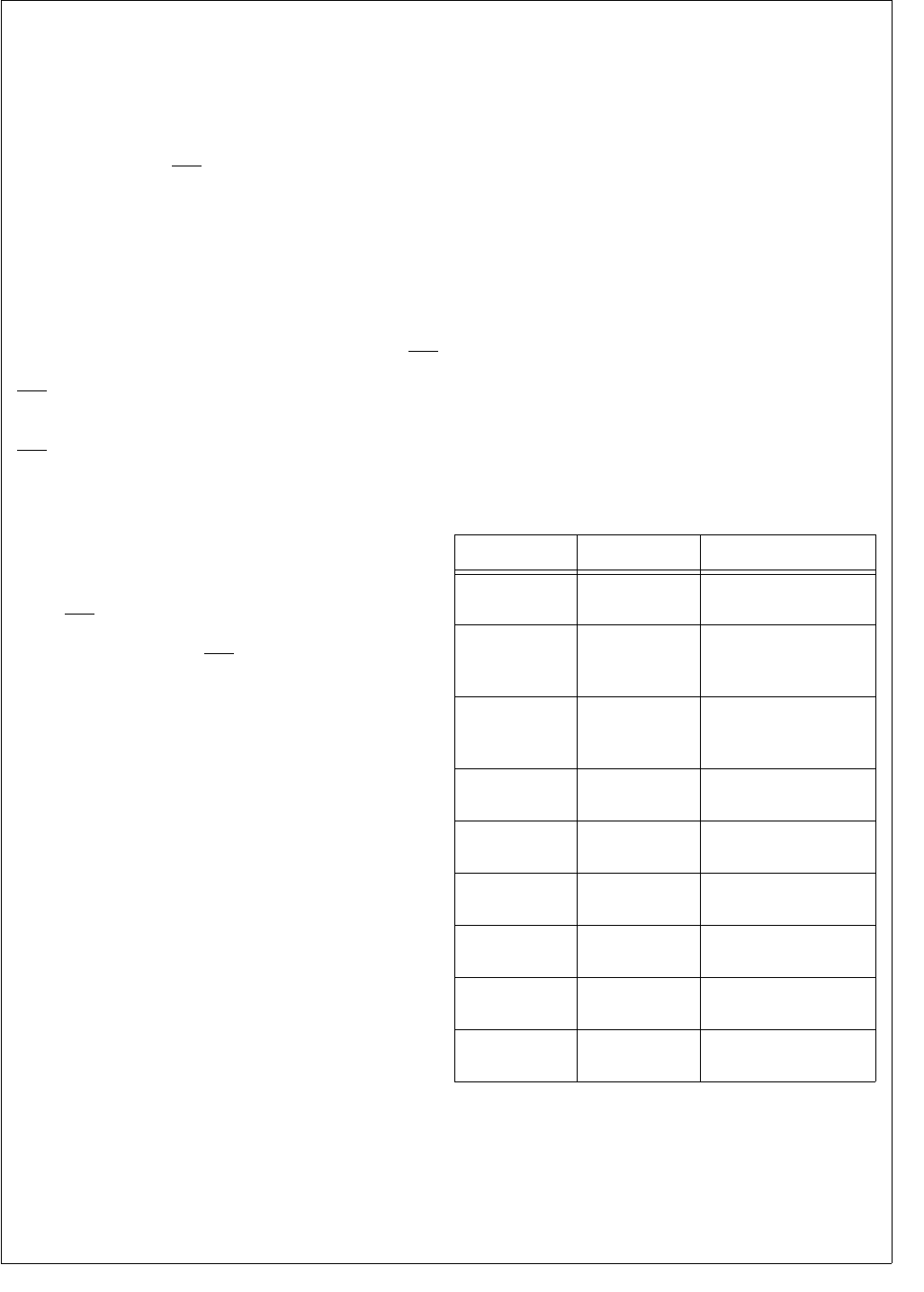

10.3 INTERRUPT CONTROLLER REGISTERS

Table 19 lists the ICU registers.

Table 19 Interrupt Controller Registers

Name Address Description

IVCT FF FE00h

Interrupt Vector

Register

NMISTAT FF FE02h

Non-Maskable

Interrupt Status

Register

EXNMI FF FE04h

External NMI Trap

Control and Status

Register

ISTAT0 FF FE0Ah

Interrupt Status

Register 0

ISTAT1 FF FE0Ch

Interrupt Status

Register 1

ISTAT2 FF FE20h

Interrupt Status

Register 2

IENAM0 FF FE0Eh

Interrupt Enable and

Mask Register 0

IENAM1 FF FE10h

Interrupt Enable and

Mask Register 1

IENAM2 FF FE22h

Interrupt Enable and

Mask Register 2