21 www.national.com

CP3BT26

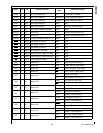

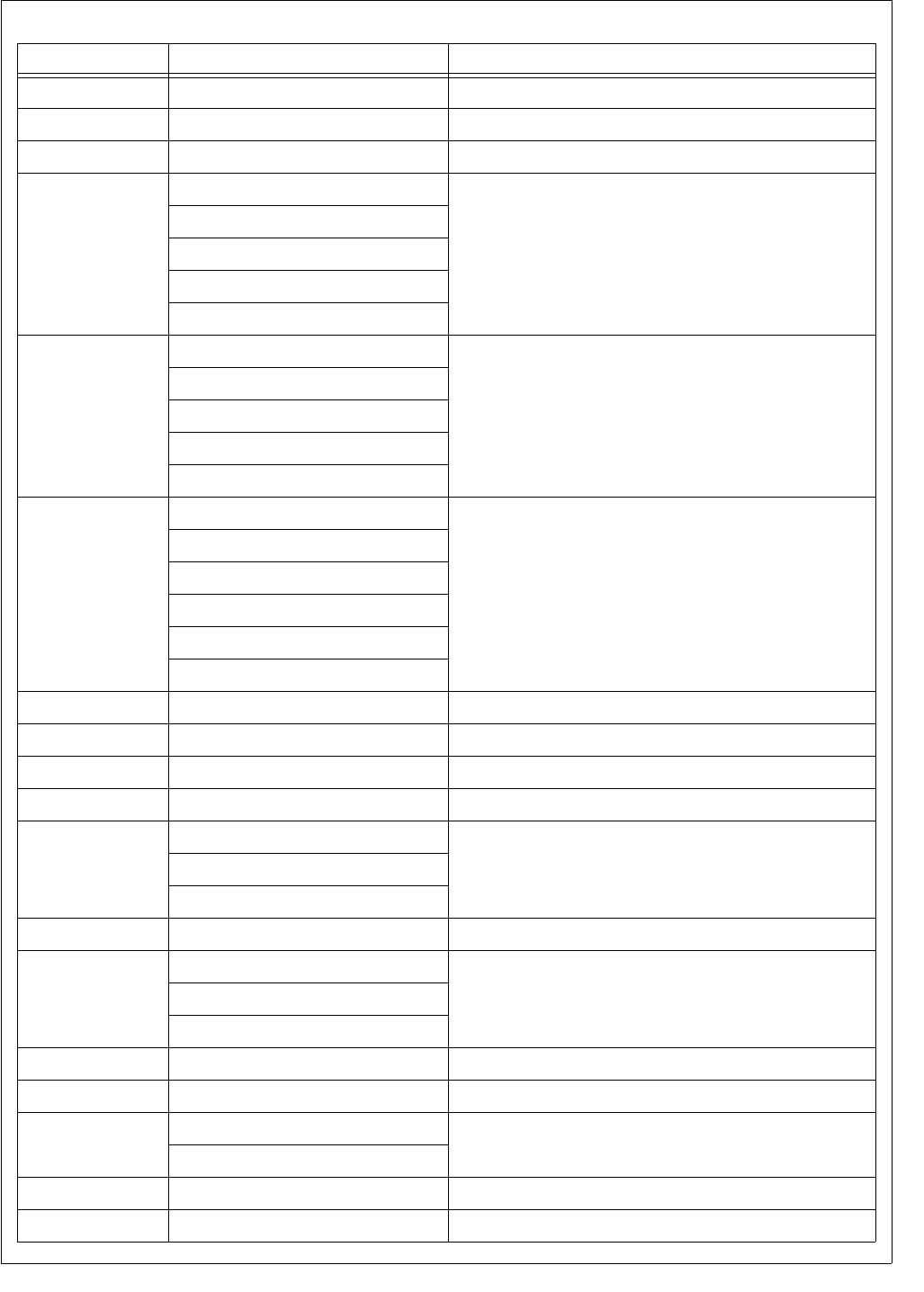

ASHUD Rsrc/imm, RPdest Arithmetic left/right shift

LSHi Rsrc/imm, Rdest Logical left/right shift

LSHD Rsrc/imm, RPdest Logical left/right shift

SBITi Iposition, disp(Rbase) Set a bit in memory

(Because this instruction treats the destination as a read-

modify-write operand, it not be used to set bits in write-

only registers.)

Iposition, disp(RPbase)

Iposition, (Rindex)disp(RPbasex)

Iposition, abs

Iposition, (Rindex)abs

CBITi Iposition, disp(Rbase) Clear a bit in memory

Iposition, disp(RPbase)

Iposition, (Rindex)disp(RPbasex)

Iposition, abs

Iposition, (Rindex)abs

TBIT

TBITi

Rposition/imm, Rsrc Test a bit in a register

Test a bit in memory

Iposition, disp(Rbase)

Iposition, disp(RPbase)

Iposition, (Rindex)disp(RPbasex)

Iposition, abs

Iposition, (Rindex)abs

LPR Rsrc, Rproc Load processor register

LPRD RPsrc, Rprocd Load double processor register

SPR Rproc, Rdest Store processor register

SPRD Rprocd, RPdest Store 32-bit processor register

Bcond disp9 Conditional branch

disp17

disp24

BAL RPlink, disp24 Branch and link

BR disp9 Branch

disp17

disp24

EXCP vector Trap (vector)

Jcond RPtarget Conditional Jump to a large address

JAL RA, RPtarget, Jump and link to a large address

RPlink, RPtarget

JUMP RPtarget Jump

JUSR RPtarget Jump and set PSR.U

Table 5 Instruction Set Summary

Mnemonic Operands Description