171 www.national.com

CP3BT26

UBKD The Break Detect bit indicates when a line

break condition occurs. This condition is de-

tected if RXD remains low for at least ten bit

times after a missing stop bit has been detect-

ed at the end of a frame. The hardware auto-

matically clears the UBKD bit on reading the

UnSTAT register, but only if the break condi-

tion on RXD no longer exists. If reading the

UnSTAT register does not clear the UBKD bit

because the break is still actively driven on

the line, the hardware clears the bit as soon as

the break condition no longer exists (when the

RXD input returns to a high level).

0 – No break condition occurred.

1 – Break condition occurred.

URB9 The Received 9th Data Bit holds the ninth

data bit, when the UART is configured to op-

erate in the 9-bit data format.

UXMIP The Transmit In Progress bit indicates when

the UART is transmitting. The hardware sets

this bit when the UART is transmitting data

and clears the bit at the end of the last frame

bit.

0 – UART is not transmitting.

1 – UART is transmitting.

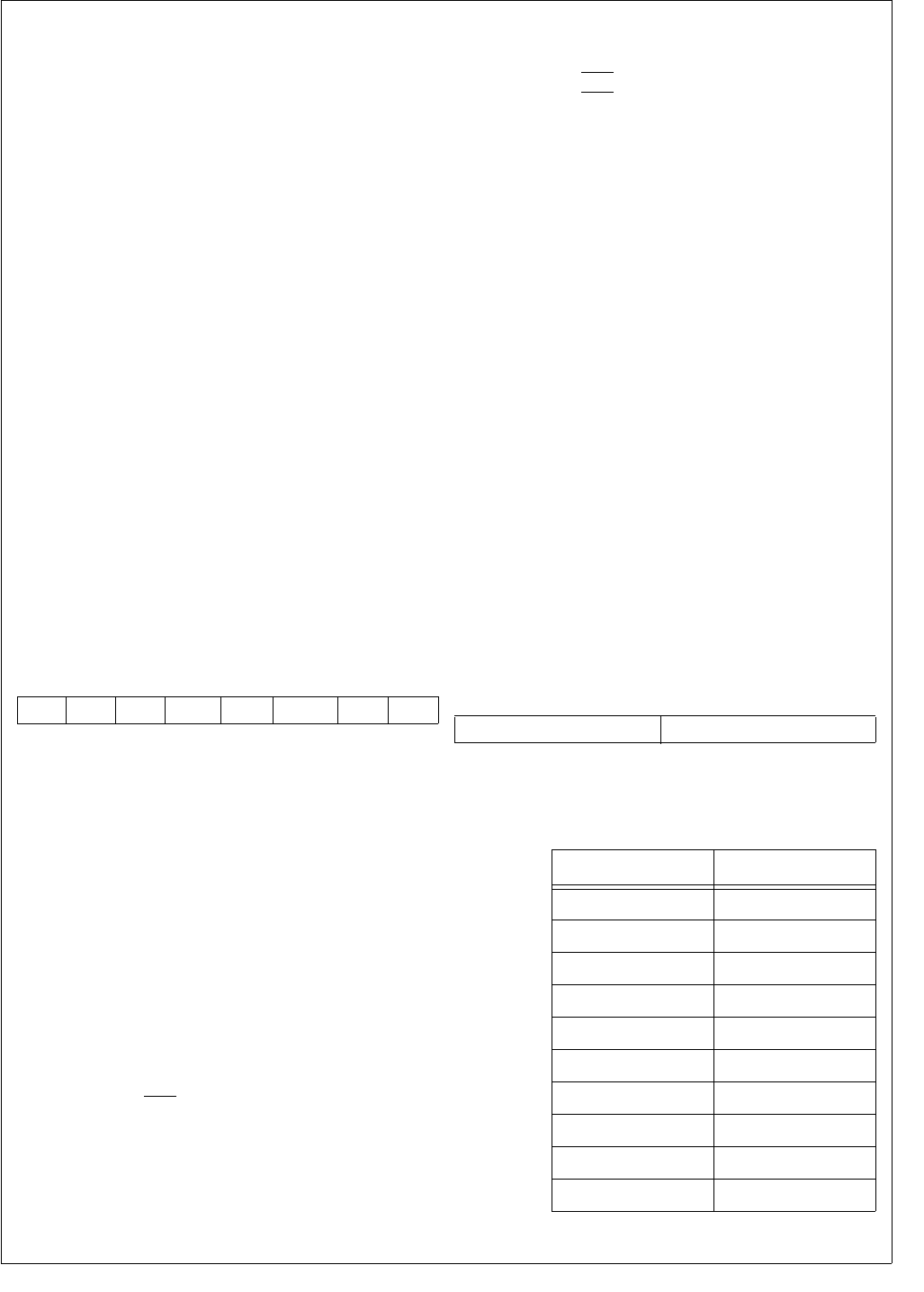

22.3.8 UART Interrupt Control Register (UnICTRL)

The UnICTRL register is a byte-wide register that contains

the receive and transmit interrupt status bits (read-only bits)

and the interrupt enable bits (read/write bits). The register is

initialized to 01h at reset. The register format is shown be-

low.

UTBE The Transmit Buffer Empty bit is set by hard-

ware when the UART transfers data from the

UnTBUF register to the transmit shift register

for transmission. It is automatically cleared by

the hardware on the next write to the UnTBUF

register.

0 – Transmit buffer is loaded.

1 – Transmit buffer is empty.

URBF The Receive Buffer Full bit is set by hardware

when the UART has received a complete data

frame and has transferred the data from the

receive shift register to the UnRBUF register.

It is automatically cleared by the hardware

when the UnRBUF register is read.

0 – Receive buffer is empty.

1 – Receive buffer is loaded.

UDCTS The Delta Clear To Send bit indicates whether

the CTS

input has changed state since the

CPU last read this register. This functionality

is only available for the UART0 module.

0 – No change since last read.

1 – State has changed since last read.

UCTS The Clear To Send bit indicates the state on

the CTS input. This functionality is only avail-

able for the UART0 module.

0 – CTS

input is high.

1 – CTS input is low.

UEFCI The Enable Flow Control Interrupt bit controls

whether a flow control interrupt is generated

when the UDCTS bit changes from clear to

set. This functionality is only available for the

UART0 module.

0 – Flow control interrupt disabled.

1 – Flow control interrupt enabled.

UETI The Enable Transmitter Interrupt bit, when

set, enables generation of an interrupt when

the hardware sets the UTBE bit.

0 – Transmit buffer empty interrupt disabled.

1 – Transmit buffer empty interrupt enabled.

UERI The Enable Receiver Interrupt bit, when set,

enables generation of an interrupt when the

hardware sets the URBF bit.

0 – Receive buffer full interrupt disabled.

1 – Receive buffer full interrupt enabled.

UEEI The Enable Receive Error Interrupt bit, when

set, enables generation of an interrupt when

the hardware sets the UERR bit in the Un-

STAT register.

0 – Receive error interrupt disabled.

1 – Receive error interrupt enabled.

22.3.9 UART Oversample Rate Register (UnOVR)

The UnOVR register is a byte-wide, read/write register that

specifies the oversample rate. At reset, the UnOVR register

is cleared. The register format is shown below.

UOVSR The Oversampling Rate field specifies the

oversampling rate, as given in the following ta-

ble.

7 6 5 4 3 2 1 0

UEEI UERI UETI UEFCI UCTS UDCTS

URBF

UTBE

7 4 3 0

Reserved UOVSR

UOVSR3:0 Oversampling Rate

0000–0110 16

0111 7

1000 8

1001 9

1010 10

1011 11

1100 12

1101 13

1110 14

1111 15