3 www.national.com

CP3BT26

2.0 Features

CPU Features

Fully static RISC processor core, capable of operating

from 0 to 24 MHz with zero wait/hold states

Minimum 41.7 ns instruction cycle time with a 24-MHz in-

ternal clock frequency, based on a 12-MHz external input

47 independently vectored peripheral interrupts

On-Chip Memory

256K bytes reprogrammable Flash program memory

8K bytes Flash data memory

32K bytes of static RAM data memory

Addresses up to 12M bytes of external memory

Broad Range of Hardware Communications Peripherals

Bluetooth Lower Link Controller (LLC) including a shared

4.5K byte Bluetooth RAM and 1K byte Bluetooth Se-

quencer RAM

Universal Serial Bus (USB) 1.1 full-speed node

ACCESS.bus serial bus (compatible with Philips I

2

C bus)

CAN interface with 15 message buffers conforming to

CAN specification 2.0B active

8/16-bit SPI, Microwire/Plus serial interface

Four-channel Universal Asynchronous Receiver/Trans-

mitter (UART), one channel has USART capability

Advanced Audio Interface (AAI) to connect to external 8/

13-bit PCM Codecs as well as to ISDN-Controllers

through the IOM-2 interface (slave only)

CVSD/PCM converter supporting one bidirectional audio

connection

General-Purpose Hardware Peripherals

12-bit A/D Converter (ADC)

Dual 16-bit Multi-Function Timer (MFT)

Versatile Timer Unit with four subsystems (VTU)

Four-channel DMA controller

Timing and Watchdog Unit

Random Number Generator peripheral

Extensive Power and Clock Management Support

On-chip Phase Locked Loop

Support for multiple clock options

Dual clock and reset

Power-down modes

Flexible I/O

Up to 54 general-purpose I/O pins (shared with on-chip

peripheral I/O)

Programmable I/O pin characteristics: TRI-STATE out-

put, push-pull output, weak pull-up input, high-imped-

ance input

Schmitt triggers on general-purpose inputs

Multi-Input Wake-Up (MIWU) capability

Power Supply

I/O port operation at 2.5V to 3.3V

Core logic operation at 2.5V

On-chip power-on reset

Temperature Range

-40°C to +85°C (Industrial)

Packages

LQFP-128, LQFP-144

Complete Development Environment

Pre-integrated hardware and software support for rapid

prototyping and production

Integrated environment

Project manager

Multi-file C source editor

High-level C source debugger

Comprehensive, integrated, one-stop technical support

Bluetooth Protocol Stack

Applications can interface to the high-level protocols or

directly to the low-level Host Controller Interface (HCI)

Transport layer support allows HCI command-based in-

terface over UART port

Baseband (Link Controller) hardware minimizes the

bandwidth demand on the CPU

Link Manager (LM)

Logical Link Control and Adaptation Protocol (L2CAP)

Service Discovery Protocol (SDP)

RFCOMM Serial Port Emulation Protocol

All packet types, piconet, and scatternet functionality

supported

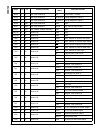

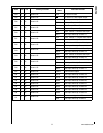

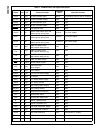

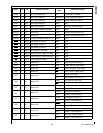

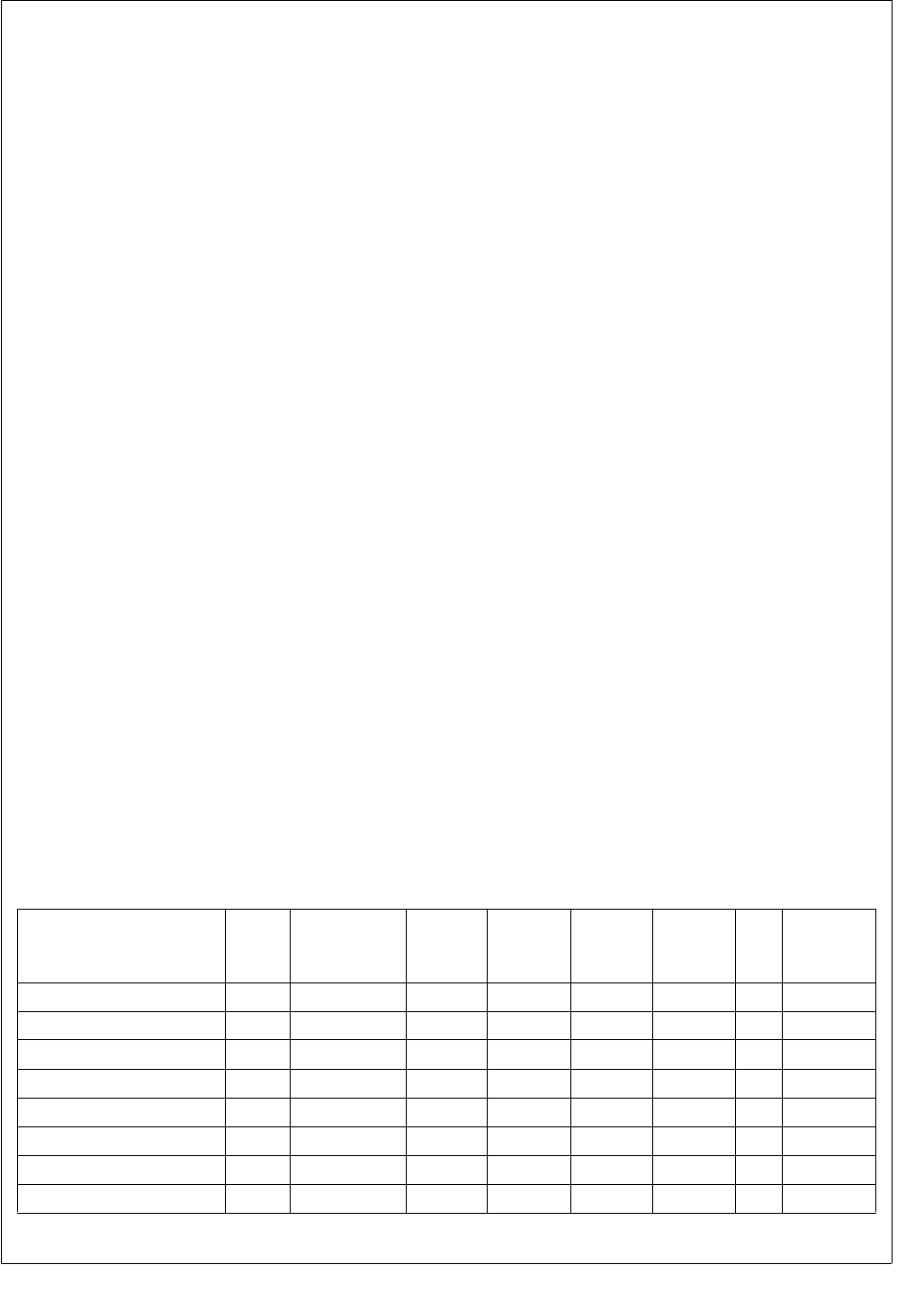

CP3BT26 Connectivity Processor Selection Guide

NSID

Speed

(MHz)

Temp. Range

Program

Flash

(Kbytes)

Data

Flash

(Kbytes)

SRAM

(Kbytes)

External

Address

Lines

I/Os

Package

Type

CP3BT26G18NEP 24 -40° to +85°C 256 8 32 0 54 LQFP-128

CP3BT26G18NEPNOPB 24 -40° to +85°C 256 8 32 0 54 LQFP-128

CP3BT26G18NEPX 24 -40° to +85°C 256 8 32 0 54 LQFP-128

CP3BT26G18NEPXNOPB 24 -40° to +85°C 256 8 32 0 54 LQFP-128

CP3BT26Y98NEP 24 -40° to +85°C 256 8 32 23 48 LQFP-144

CP3BT26Y98NEPNOPB 24 -40° to +85°C 256 8 32 23 48 LQFP-144

CP3BT26Y98NEPX 24 -40° to +85°C 256 8 32 23 48 LQFP-144

CP3BT26Y98NEPXNOPB 24 -40° to +85°C 256 8 32 23 48 LQFP-144

NEP - Erased part (Bluetooth device address in Information Block 1); X - Tape and reel; NOPB - No lead solder