www.national.com 258

CP3BT26

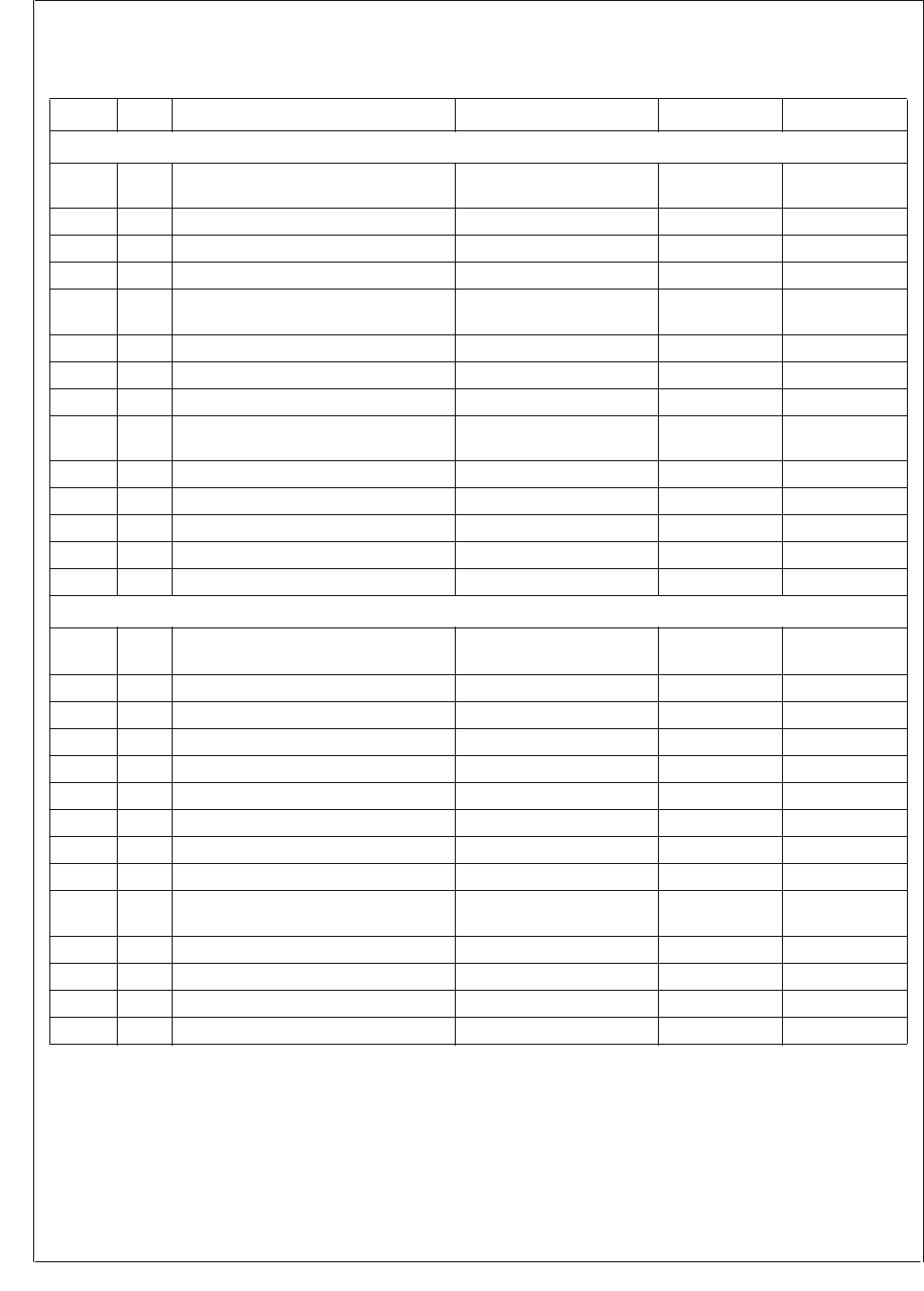

30.12 ACCESS.BUS TIMING

Table 89 ACCESS.bus Signals

Symbol

Figure

Description Reference Min (ns) Max (ns)

ACCESS.bus Input Signals

t

BUFi

126

Bus free time between Stop and Start

Condition

t

SCLhigho

-

t

CSTOsi

126

SCL setup time Before Stop Condition (8 × t

CLK

)

- t

SCLri

-

t

CSTRhi

126

SCL hold time After Start Condition (8 × t

CLK

)

- t

SCLri

-

t

CSTRsi

126

SCL setup time Before Start Condition (8 × t

CLK

)

- t

SCLri

-

t

DHCsi

127

Data High setup time

Before SCL Rising Edge

(RE)

2 × t

CLK

-

t

DLCsi

126

Data Low setup time Before SCL RE 2 × t

CLK

-

t

SCLfi

125

SCL signal rise time - 300

t

SCLri

125

SCL signal fall time - 1000

t

SCLlowi

128

SCL low time

After SCL Falling Edge

(FE)

16 × t

CLK

-

t

SCLhighi

128

SCL high time After SCL RE 16 × t

CLK

-

t

SDAri

125

SDA signal rise time - 1000

t

SDAfl

125

SDA signal fall time - 300

t

SDAhi

128

SDA hold time After SCL FE 0 -

t

SDAsi

128

SDA setup time Before SCL RE 2 × t

CLK

-

ACCESS.bus Output Signals

t

BUFo

126

Bus free time between Stop and Start

Condition

t

SCLhigho

t

CSTOso

126

SCL setup time Before Stop Condition t

SCLhigho

t

CSTRho

126

SCL hold time After Start Condition t

SCLhigho

t

CSTRso

127

SCL setup time Before Start Condition t

SCLhigho

t

DHCso

127

Data High setup time Before SCL R.E. t

SCLhigho

-t

SDAro

t

DLCso

126

Data Low setup time Before SCL R.E. t

SCLhigho

-t

SDAfo

t

SCLfo

125

SCL signal Fall time 300

c

t

SCLro

125

SCL signal Rise time -

d

t

SCLlowo

128

SCL low time After SCL F.E. (K × t

CLK

) -1

e

t

SCLhigh

o

128

SCL high time After SCL R.E. (K × t

CLK

) -1

e

t

SDAfo

125

SDA signal Fall time 300

t

SDAro

125

SDA signal Rise time

-

t

SDAho

128

SDA hold time After SCL F.E.

(7 × t

CLK

) - t

SCLfo

t

SDAvo

128

SDA valid time After SCL F.E. (7 × t

CLK

) + t

RD