www.national.com 154

CP3BT26

IOM2 The IOM-2 Mode bit selects the normal PCM

interface mode or a special IOM-2 mode used

to connect to external ISDN controller devic-

es. The AAI can only operate as a slave in the

IOM-2 mode, i.e. the bit clock and frame sync

signals are provided by the ISDN controller. If

the IOM2 bit is clear, the AAI operates in the

normal PCM interface mode used to connect

to external PCM codecs and other PCM audio

devices.

0 – IOM-2 mode disabled.

1 – IOM-2 mode enabled.

AAIEN The AAI Enable bit controls whether the Ad-

vanced Audio Interface is enabled. All AAI

registers provide read/write access while

(CLKEN = 1) AAIEN is clear. The AAIEN bit is

clear after reset.

0 – AAI module disabled.

1 – AAI module enabled.

CLKEN The Clock Enable bit controls whether the Ad-

vanced Audio Interface clock is enabled. The

CLKEN bit must be set to allow access to any

AAI register. It must also be set before any

other bit of the AGCR can be set. The CLKEN

bit is clear after reset.

0 – AAI module clock disabled.

1 – AAI module clock enabled.

20.7.6 Audio Interrupt Status and Control Register

(AISCR)

The ASCR register is used to specify the source and the

conditions, when the audio interface interrupt is asserted to

the Interrupt Control Unit. It also holds the interrupt pending

bits and the corresponding interrupt clear bits for each audio

interface interrupt source. The CPU bus master has read/

write access to the ASCR register. After reset, this register

is clear.

RXIE The Receive Interrupt Enable bit controls

whether receive interrupts are generated. If

the RXIE bit is clear, no receive interrupt will

be generated.

0 – Receive interrupt disabled.

1 – Receive interrupt enabled.

RXEIE The Receive Error Interrupt Enable bit con-

trols whether receive error interrupts are gen-

erated. Setting this bit enables a receive error

interrupt, when the Receive Buffer Overrun

(RXOR) bit is set. If the RXEIE bit is clear, no

receive error interrupt will be generated.

0 – Receive error interrupt disabled.

1 – Receive error interrupt enabled.

TXIE The Transmit Interrupt Enable bit controls

whether transmit interrupts are generated.

Setting this bit enables a transmit interrupt,

when the Transmit Buffer Almost Empty (TX-

AE) bit is set. If the TXIE bit is clear, no inter-

rupt will be generated.

0 – Transmit interrupt disabled.

1 – Transmit interrupt enabled.

TXEIE The Transmit Error Interrupt Enable bit con-

trols whether transmit error interrupts are gen-

erated. Setting this bit to 1 enables a transmit

error interrupt, when the Transmit Buffer Un-

derrun (TXUR) bit is set. If the TXEIE bit is

clear, no transmit error interrupt will be gener-

ated.

0 – Transmit error interrupt disabled.

1 – Transmit error interrupt enabled.

RXIP The Receive Interrupt Pending bit indicates

that a receive interrupt is currently pending.

The RXIP bit is cleared by writing a 1 to the

RXIC bit. The RXIP bit provides read-only ac-

cess.

0 – No receive interrupt pending.

1 – Receive interrupt pending.

RXEIP The Receive Error Interrupt Pending bit indi-

cates that a receive error interrupt is currently

pending. The RXEIP bit is cleared by writing a

1 to the RXEIC bit. The RXEIP bit provides

read-only access.

0 – No receive error interrupt pending.

1 – Receive error interrupt pending.

TXIP The Transmit Interrupt Pending bit indicates

that a transmit interrupt is currently pending.

The TXIP bit is cleared by writing a 1 to the

TXIC bit. The TXIP bit provides read-only ac-

cess.

0 – No transmit interrupt pending.

1 – Transmit interrupt pending.

TXEIP Transmit Error Interrupt Pending. This bit indi-

cates that a transmit error interrupt is currently

pending. The TXEIP bit is cleared by software

by writing a 1 to the TXEIC bit. The TXEIP bit

provides read-only access.

0 – No transmit error interrupt pending.

1 – Transmit error interrupt pending.

RXIC The Receive Interrupt Clear bit is used to

clear the RXIP bit.

0 – Writing a 0 to the RXIC bit is ignored.

1 – Writing a 1 clears the RXIP bit.

RXEIC The Receive Error Interrupt Clear bit is used

to clear the RXEIP bit.

0 – Writing a 0 to the RXEIC bit is ignored.

1 – Writing a 1 clears the RXEIP bit.

TXIC The Transmit Interrupt Clear bit is used to

clear the TXIP bit.

0 – Writing a 0 to the TXIC bit is ignored.

1 – Writing a 1 clears the TXIP bit.

TXEIC The Transmit Error Interrupt Clear bit is used

to clear the TXEIP bit.

0 – Writing a 0 to the TXEIC bit is ignored.

1 – Writing a 1 clears the TXEIP bit.

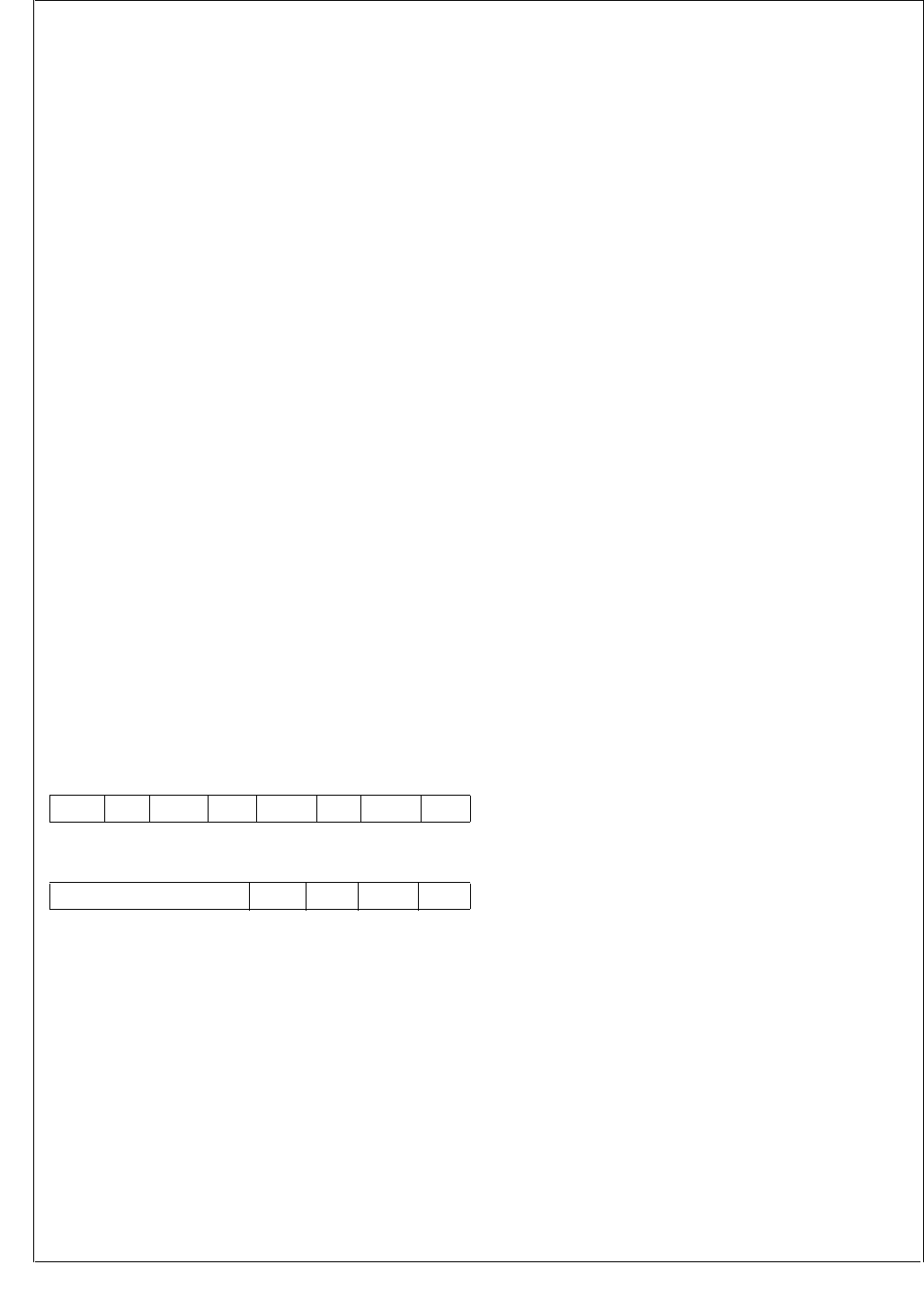

7 6 5 4 3 2 1 0

TXEIP TXIP RXEIP RXIP TXEIE TXIE RXEIE RXIE

15 12 11 10 9 8

Reserved TXEIC TXIC RXEIC RXIC