149 www.national.com

CP3BT26

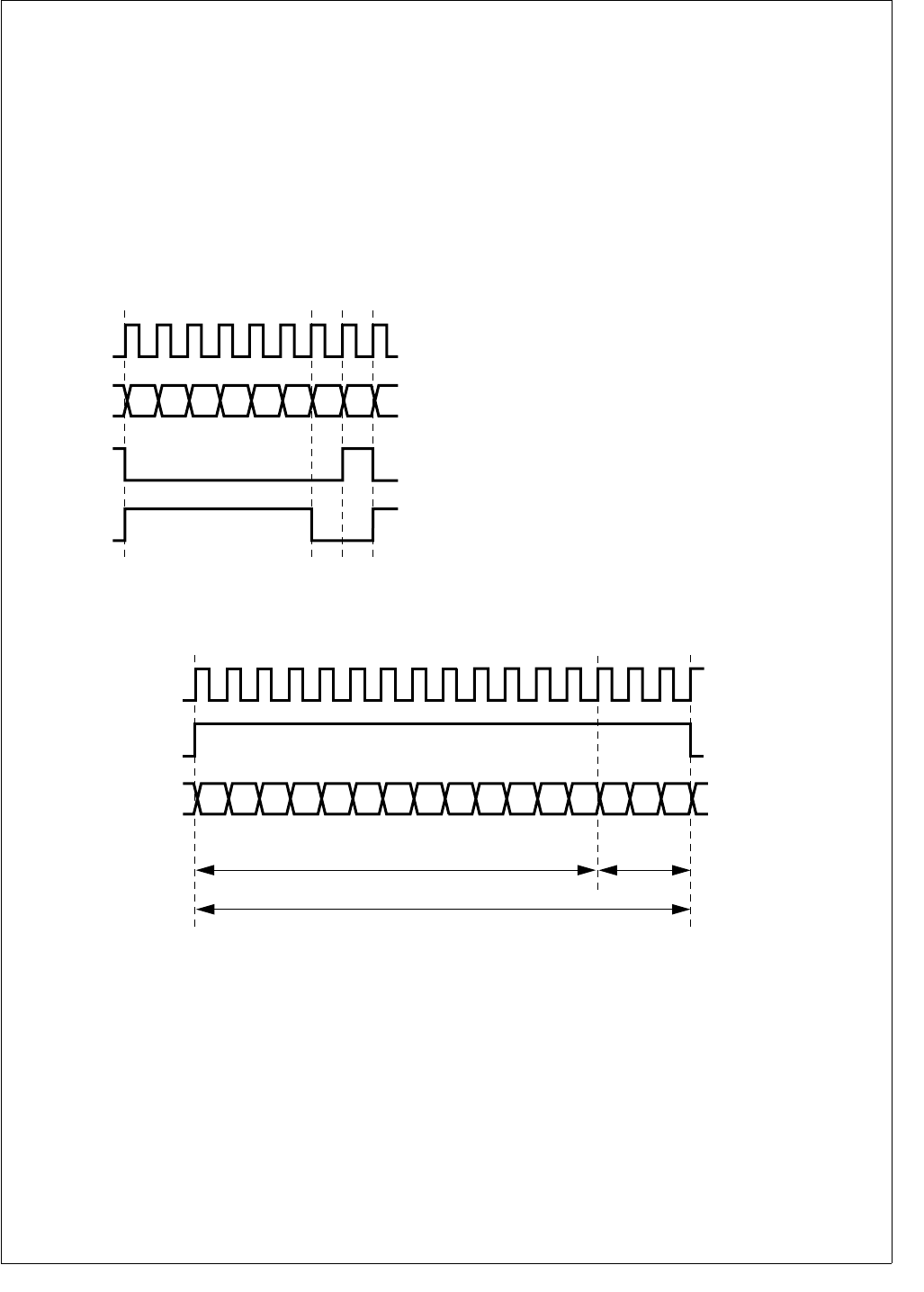

If the corresponding Frame Sync Select (FSS) bit in the Au-

dio Control and Status register is set, the receive and/or

transmit path generates or recognizes long frame sync puls-

es. For 8-bit data, the frame sync pulse generated will be 6

bit shift clock periods long, and for 16-bit data the frame

sync pulse can be configured to be 13, 14, 15, or 16 bit shift

clock periods long. When receiving frame sync, it should be

active on the first bit of data and stay active for a least two

bit clock periods. It must go low for at least one bit clock pe-

riod before starting a new frame. When long frame sync

pulses are used, the transfer of the first word (first slot) be-

gins at the first positive edge of the bit shift clock after the

positive edge of the frame sync pulse. Figure 71 shows ex-

amples of short and long frame sync pulses.

Figure 71. Short and Long Frame Sync Pulses

Some codecs require an inverted frame sync signal. This is

available by setting the Inverted Frame Sync bit in the

AGCR register.

20.6.3 Audio Control Data

The audio interface provides the option to fill a 16-bit slot

with up to three data bits if only 13, 14, or 15 PCM data bits

are transmitted. These additional bits are called audio con-

trol data and are appended to the PCM data stream. The

AAI can be configured to append either 1, 2, or 3 audio con-

trol bits to the PCM data stream. The number of audio data

bits to be used is specified by the 2-bit Audio Control On

(ACO) field. If the ACO field is not equal to 0, the specified

number of bits are taken from the Audio Control Data field

(ACD) and appended to the data stream during every trans-

mit operation. The ADC0 bit is the first bit added to the

transmit data stream after the last PCM data bit. Typically,

these bits are used for gain control, if this feature is support-

ed by the external PCM codec.Figure 72 shows a 16-bit slot

comprising a 13-bit PCM data word plus three audio control

bits.

Figure 72. Audio Slot with Audio Control Data

D7D6D5D4D3D2D1D0

Long Frame

Sync Pulse

Bit Shift Clock

(SCK/SRCLK)

Shift Data

(STD/SRD)

DS156

Short Frame

Sync Pulse

D7D6D5D4D3D2D1D0

SCK

STD

DS161

SFS

ACD0ACD1ACD2D12D11D10D9D8

13-bit PCM Data Word

Audio

Control

Bits

16-bit Slot