197 www.national.com

CP3BT26

Counter Clock Source Select

There are two clock source selectors that allow software to

independently select the clock source for each of the two

16-bit counters from any one of the following sources:

No clock (which stops the counter)

Prescaled System Clock

External event count based on TB

Pulse accumulate mode based on TB

Slow Clock (derived from the low-frequency oscillator or

divided from the high-speed oscillator)

Prescaler

The 5-bit clock prescaler allows software to run the timer

with a prescaled clock signal. The prescaler consists of a 5-

bit read/write prescaler register (TPRSC) and a 5-bit down

counter. The System Clock is divided by the value contained

in the prescaler register plus 1. Therefore, the timer clock

period can be set to any value from 1 to 32 divisions of the

System Clock period. The prescaler register and down

counter are both cleared upon reset.

External Event Clock

The TB I/O pin can be configured to operate as an external

event input clock for either of the two 16-bit counters. This

input can be programmed to detect either rising or falling

edges. The minimum pulse width of the external signal is

one System Clock cycle. This means that the maximum fre-

quency at which the counter can run in this mode is one-half

of the System Clock frequency. This clock source is not

available in the capture modes (modes 2 and 4) because

the TB pin is used as one of the two capture inputs.

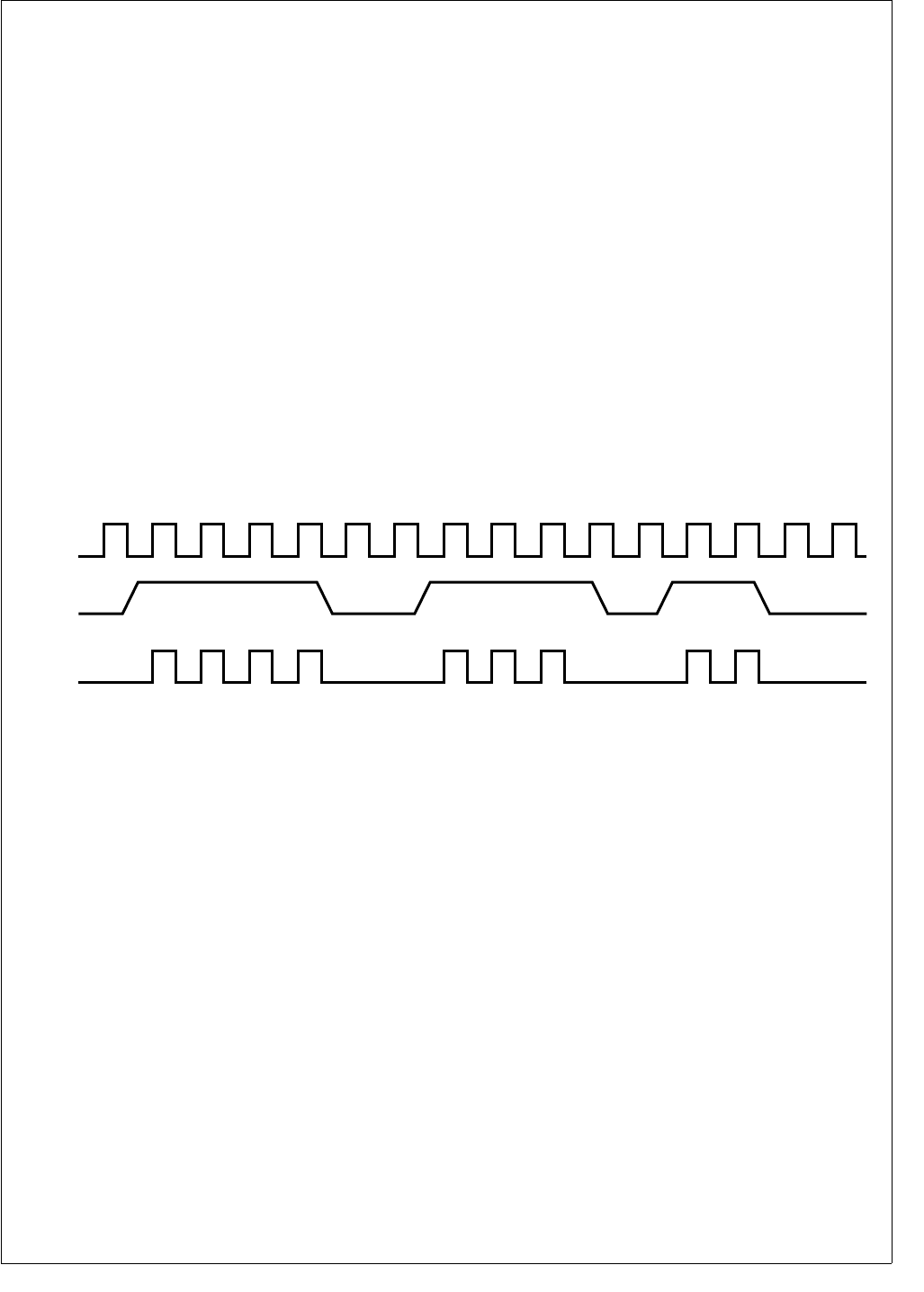

Pulse Accumulate Mode

The counter can also be configured to count prescaler out-

put clock pulses when the TB input is high and not count

when the TB input is low, as illustrated in Figure 99. The re-

sulting count is an indicator of the cumulative time that the

TB input is high. This is called the “pulse-accumulate”

mode. In this mode, an AND gate generates a clock signal

for the counter whenever a prescaler clock pulse is generat-

ed and the TB input is high. (The polarity of the TB signal is

programmable, so the counter can count when the TB input

is low rather than high.) The pulse-accumulate mode is not

available in the capture modes (modes 2 and 4) because

the TB pin is used as one of the two capture inputs.

Figure 99. Pulse-Accumulate Mode

Slow Clock

The Slow Clock is generated by the Triple Clock and Reset

module. The clock source is either the divided fast clock or

the external 32.768 kHz crystal oscillator (if available and

selected). The Slow Clock can be used as the clock source

for the two 16-bit counters. Because the Slow Clock can be

asynchronous to the System Clock, a circuit is provided to

synchronize the clock signal to the high-frequency System

Clock before it is used for clocking the counters. The syn-

chronization circuit requires that the Slow Clock operate at

no more than one-fourth the speed of the System Clock.

Limitations in Low-Power Modes

The Power Save mode uses the Slow Clock as the System

Clock. In this mode, the Slow Clock cannot be used as a

clock source for the timers because that would drive both

clocks at the same frequency, and the clock ratio needed for

synchronization to the System Clock would not be main-

tained. However, the External Event Clock and Pulse Accu-

mulate Mode will still work, as long as the external event

pulses are at least the size of the whole slow-clock period.

Using the prescaled System Clock will also work, but at a

much slower rate than the original System Clock.

Idle and Halt modes stop the System Clock (the high-fre-

quency and/or low-frequency clock) completely. If the Sys-

tem Clock is stopped, the timer stops counting until the

System Clock resumes operation.

In the Idle or Halt mode, the System Clock stops completely,

which stops the operation of the timers. In that case, the tim-

ers stop counting until the System Clock resumes operation.

26.2 TIMER OPERATING MODES

Each timer/counter unit can be configured to operate in any

of the following modes:

Processor-Independent Pulse Width Modulation (PWM)

mode

Dual-Input Capture mode

Dual Independent Timer mode

Single-Input Capture and Single Timer mode

At reset, the timers are disabled. To configure and start the

timers, software must write a set of values to the registers

that control the timers. The registers are described in

Section 26.5.

Prescaler

Output

TB

Counter

Clock

DS083