www.national.com 48

CP3BT26

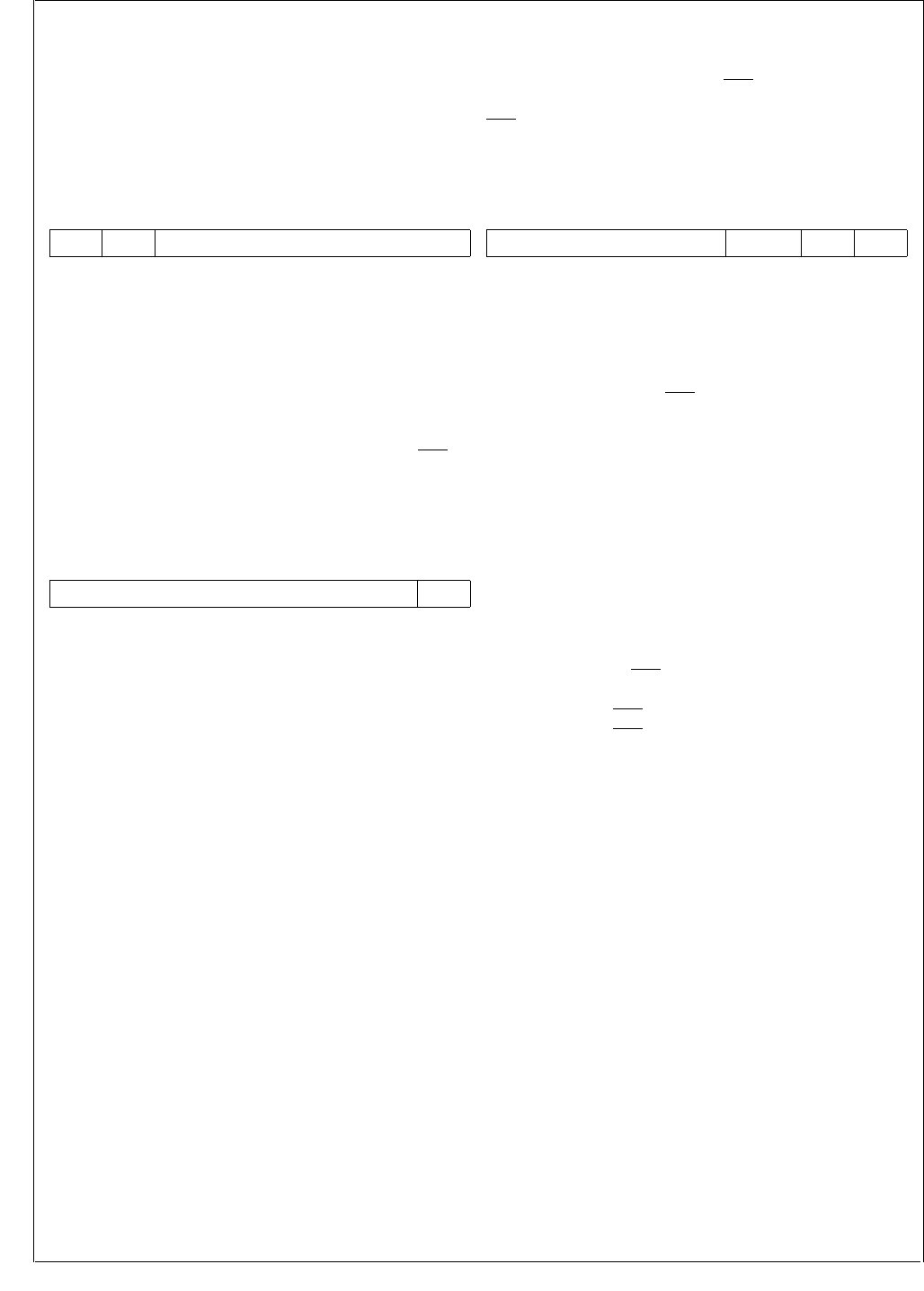

10.3.1 Interrupt Vector Register (IVCT)

The IVCT register is a byte-wide read-only register which re-

ports the encoded value of the highest priority maskable in-

terrupt that is both asserted and enabled. The valid range is

from 10h to 3Fh. The register is read by the CPU during an

interrupt acknowledge bus cycle, and INTVECT is valid dur-

ing that time. It may contain invalid data while INTVECT is

updated.

INTVECT The Interrupt Vector field indicates the highest

priority interrupt which is both asserted and

enabled.

10.3.2 Non-Maskable Interrupt Status Register

(NMISTAT)

The NMISTAT register is a byte-wide read-only register. It

holds the status of the current pending Non-Maskable Inter-

rupt (NMI) requests. On the CP3BT26, the external NMI

in-

put is the only source of NMI interrupts. The NMISTAT

register is cleared on reset and each time its contents are

read.

EXT The External NMI request bit indicates wheth-

er an external non-maskable interrupt request

has occurred. Refer to the description of the

EXNMI register below for additional details.

0

– No external NMI request.

1

– External NMI request has occurred.

10.3.3 External NMI Trap Control and Status Register

(EXNMI)

The EXNMI register is a byte-wide read/write register. It in-

dicates the current value of the NMI

pin and controls the

NMI interrupt trap generation based on a falling edge of the

NMI

pin. TST, EN and ENLCK are cleared on reset. When

writing to this register, all reserved bits must be written with

0 for the device to function properly

EN The EXNMI trap enable bit is one of two bits

that can be used to enable NMI interrupts.

The bit is cleared by hardware at reset and

whenever the NMI interrupt occurs (EXN-

MI.EXT set). It is intended for applications

where the NMI

input toggles frequently but

nested NMI traps are not desired. For these

applications, the EN bit needs to be re-en-

abled before exiting the trap handler. When

used this way, the ENLCK bit should never be

set. The EN bit can be set and cleared by soft-

ware (software can set this bit only if EXN-

MI.EXT is cleared), and should only be set

after the interrupt base register and the inter-

rupt stack pointer have been set up.

0

– NMI interrupts not enabled by this bit (but

may be enabled by the ENLCK bit).

1

– NMI interrupts enabled.

PIN The PIN bit indicates the state (non-inverted)

on the NMI input pin. This bit is read-only, data

written into it is ignored.

0

– NMI pin not asserted.

1 – NMI pin asserted.

ENLCK The EXNMI trap enable lock bit is used to per-

manently enable NMI interrupts. Only a de-

vice reset can clear the ENLCK bit. This

allows the external NMI feature to be enabled

after the interrupt base register and the inter-

rupt stack pointer have been set up. When the

ENLCK bit is set, the EN bit is ignored.

0

– NMI interrupts not enabled by this bit (but

may be enabled by the EN bit).

1

– NMI interrupts enabled.

7 6 5 0

0 0 INTVECT

710

Reserved EXT

73210

Reserved ENLCK PIN EN