www.national.com 56

CP3BT26

12.0 Power Management

The Power Management Module (PMM) improves the effi-

ciency of the CP3BT26 by changing the operating mode

(and therefore the power consumption) according to the re-

quired level of device activity. The device implements four

power modes:

Active

Power Save

Idle

Halt

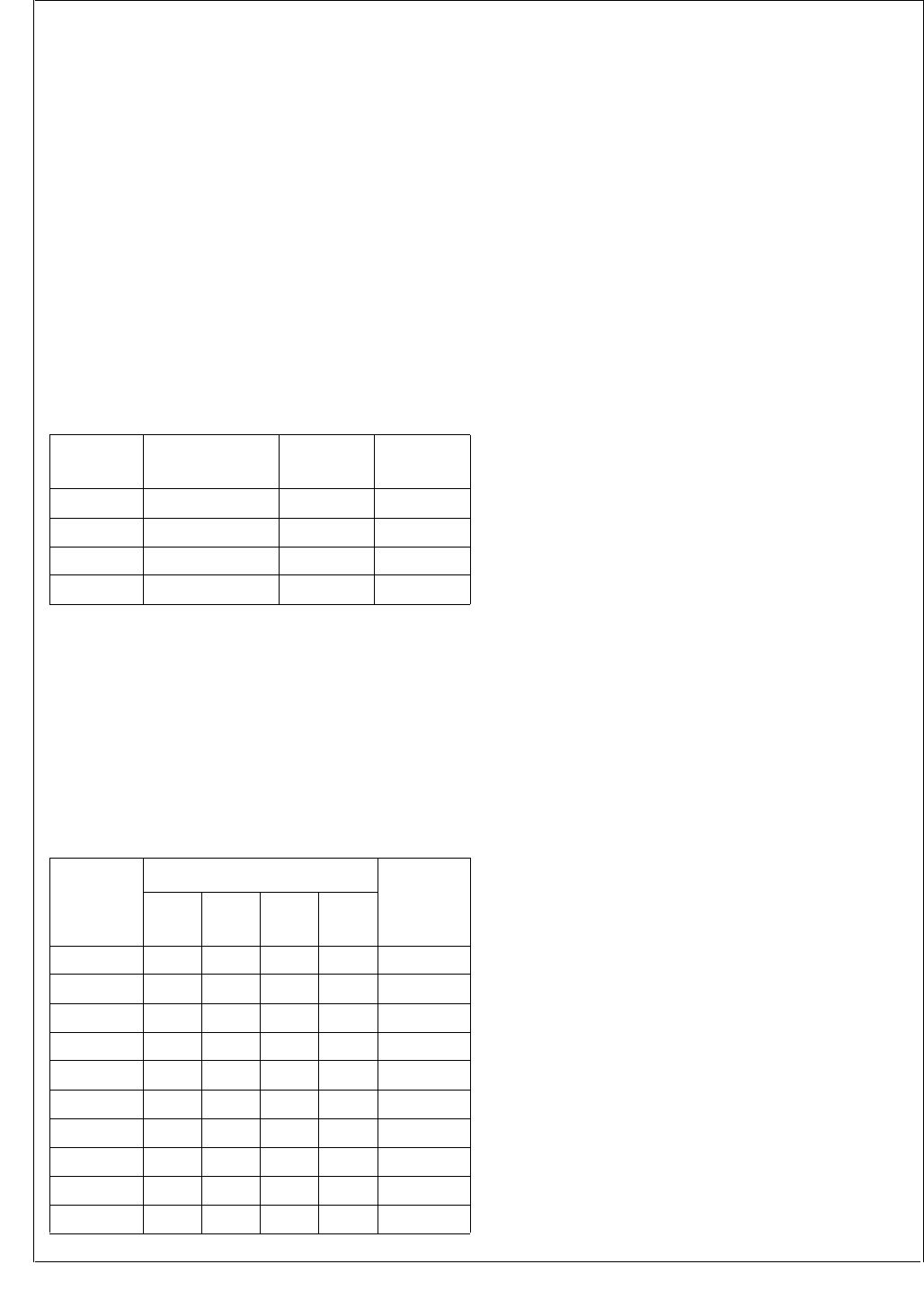

Table 24 summarizes the differences between power

modes: the state of the high-frequency oscillator (on or off),

the System Clock source (clock used by most modules),

and the clock source used by the Timing and Watchdog

Module (TWM). The high-frequency oscillator generates the

12-MHz Main Clock, and the low-frequency oscillator gener-

ates a 32.768 kHz clock. The Slow Clock can be driven by

the 32.768 kHz clock or a scaled version of the Main Clock.

The low-frequency oscillator continues to operate in all four

modes and power must be provided continuously to the de-

vice power supply pins. In Halt mode, however, Slow Clock

does not toggle, and as a result, the TWM timer and Watch-

dog Module do not operate. For the Power Save and Idle

modes, the high-frequency oscillator can be turned on or off

under software control, as long as the low-frequency oscil-

lator is used to drive Slow Clock.

Table 25 shows the clock sources used by the CP3BT26 de-

vice modules and their behavior in each power mode.

* The Analog/Digital Converter (ADC) module is not auto-

matically disabled by entering Halt mode, however its clock

is stopped so no conversions may be performed in Halt

mode. For maximum power savings, software must disable

the ADC module before entering Halt mode.

A module shown as On/Off in Table 25 may be enabled or

disabled by software. A module shown as Active continues

to operate even while its clock is suspended, which allows

wake-up events to be processed during Idle and Halt

modes.

The Random Number Generator (RNG) module has two os-

cillators which operate independently of the rest of the sys-

tem. For maximum power savings, software must disable

these oscillators.

12.1 ACTIVE MODE

In Active mode, the high-frequency oscillator is active and

generates the 12-MHz Main Clock. The 32.768 kHz oscilla-

tor is active and may be used to generate the Slow Clock.

The PLL can be active or inactive, as required. Most on-chip

modules are driven by the System Clock. The System Clock

can be the PLL Clock after a programmable divider or the

12-MHz Main Clock. The activity of peripheral modules is

controlled by their enable bits.

Power consumption can be reduced in this mode by selec-

tively disabling modules and by executing the WAIT instruc-

tion. When the WAIT instruction is executed, the CPU stops

executing new instructions until it receives an interrupt sig-

nal. After reset, the CP3BT26 is in Active Mode.

12.2 POWER SAVE MODE

In Power Save mode, Slow Clock is used as the System

Clock which drives the CPU and most on-chip modules. If

Slow Clock is driven by the 32.768 kHz oscillator and no on-

chip module currently requires the 12-MHz Main Clock, soft-

ware can disable the high-frequency oscillator to further re-

duce power consumption. Auxiliary Clocks 1 and 2 can be

turned off under software control before switching to a re-

duced power mode, or they may remain active as long as

Main Clock is also active. If the system does not require the

PLL output clock, the PLL can be disabled. Alternatively, the

Main Clock and the PLL can also be controlled by the Hard-

ware Clock Control function, if enabled. The clock architec-

ture is described in Section 11.0.

The Bluetooth LLC can either be switched to the 32 kHz

clock internally in the module, or it remains running off Aux-

iliary clock 1 as long as the Main Clock and Auxiliary Clock

1 are enabled.

In Power Save mode, some modules are disabled or their

operation is restricted. Other modules, including the CPU,

continue to function normally, but operate at a reduced clock

rate. Details of each module’s activity in Power Save mode

are described in each module’s descriptions.

It is recommended to keep CPU activity at a minimum by ex-

ecuting the WAIT instruction to guarantee low power con-

sumption in the system.

Table 24 Power Mode Operating Summary

Mode

High-Frequency

Oscillator

System

Clock

TWM Clock

Active On Main Clock Slow Clock

Power Save On or Off Slow Clock Slow Clock

Idle On or Off None Slow Clock

Halt Off None None

Table 25 Module Activity Summary

Module

Power Mode

Clock

Source

Active

Power

Save

Idle Halt

CPU On On/Off Off Off System

MIWU On On Active Active System

PMM On On On Active Slow Clock

TWM OnOnOnOffSlow Clock

USB On/Off On/Off On/Off Off PLL Clock

Bluetooth On/Off On/Off On/Off Off Aux 1 Clock

AAI On/Off On/Off On/Off Off Aux 1 Clock

CVSD/PCM On/Off On/Off On/Off Off Aux 2 Clock

ADC On/Off On/Off On/Off Off* Aux 2 Clock

All Others On/Off On/Off Off Off System