185 www.national.com

CP3BT26

Power Down

When this device is in Power Save, Idle, or Halt mode, the

ACB module is not active but retains its status. If the ACB is

enabled (ACBCTL2.ENABLE = 1) on detection of a Start

Condition, a wake-up signal is issued to the MIWU module.

Use this signal to switch this device to Active mode.

The ACB module cannot check the address byte for a match

following the start condition that caused the wake-up event

for this device. The ACB responds with a negative acknowl-

edge, and the device should resend both the Start Condition

and the address after this device has had time to wake up.

Check that the ACBCST.BUSY bit is inactive before entering

Power Save, Idle, or Halt mode. This guarantees that the de-

vice does not acknowledge an address sent and stop re-

sponding later.

24.2.3 SDA and SCL Pins Configuration

The SDA and SCL pins are driven as open-drain signals.

For more information, see the I/O configuration section.

24.2.4 ACB Clock Frequency Configuration

The ACB module permits software to set the clock frequen-

cy used for the ACCESS.bus clock. The clock is set by the

ACBCTL2.SCLFRQ field. This field determines the SCL

clock period used by this device. This clock low period may

be extended by stall periods initiated by the ACB module or

by another ACCESS.bus device. In case of a conflict with

another bus master, a shorter clock high period may be

forced by the other bus master until the conflict is resolved.

24.3 ACCESS.BUS INTERFACE REGISTERS

The ACCESS.bus interface uses the registers listed in

Ta ble 7 5.

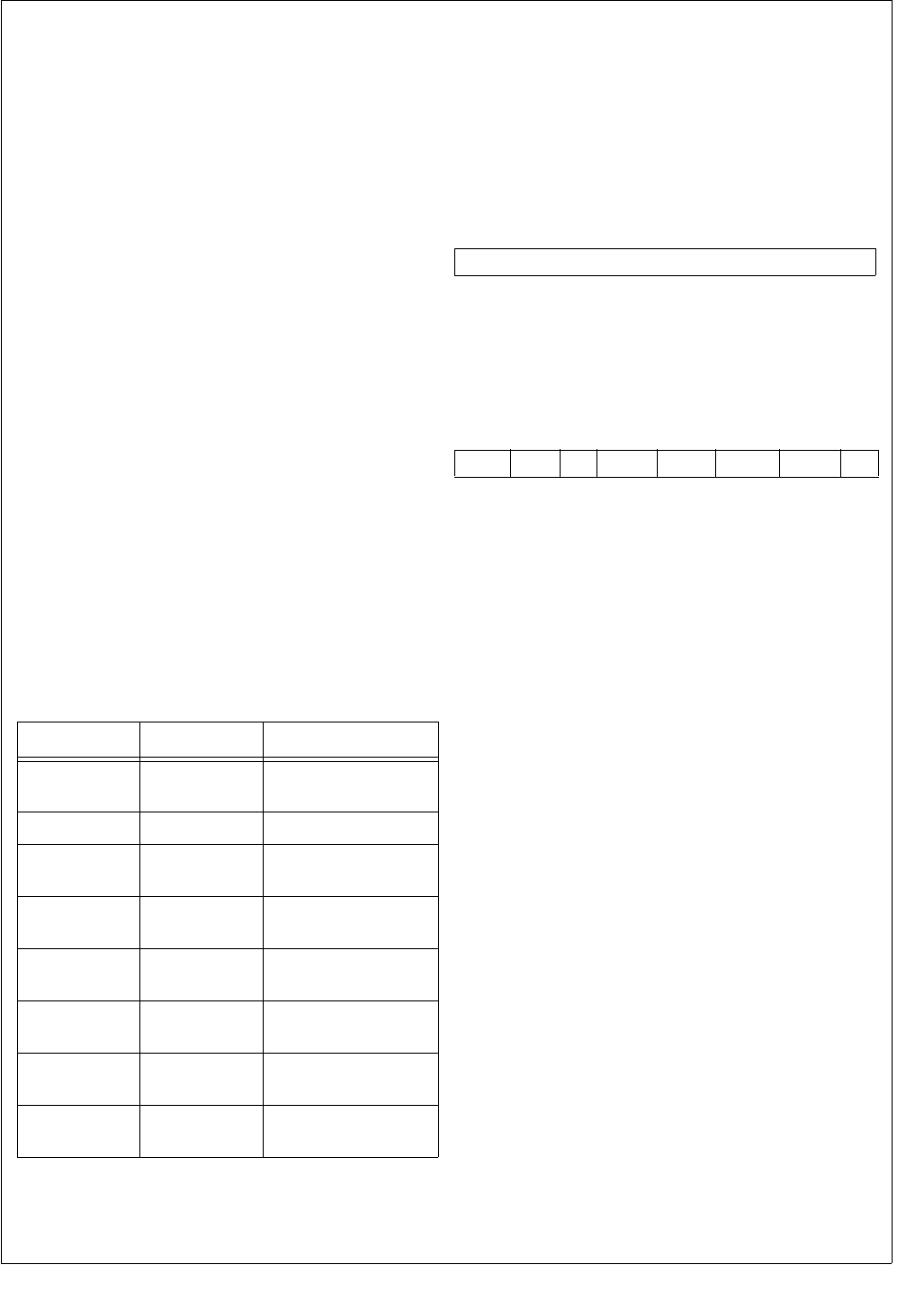

24.3.1 ACB Serial Data Register (ACBSDA)

The ACBSDA register is a byte-wide, read/write shift regis-

ter used to transmit and receive data. The most significant

bit is transmitted (received) first and the least significant bit

is transmitted (received) last. Reading or writing to the ACB-

SDA register is allowed when ACBST.SDAST is set; or for

repeated starts after setting the START bit. An attempt to

access the register in other cases produces unpredictable

results.

24.3.2 ACB Status Register (ACBST)

The ACBST register is a byte-wide, read-only register that

maintains current ACB status. At reset, and when the mod-

ule is disabled, ACBST is cleared.

XMIT The Direction Bit bit is set when the ACB mod-

ule is currently in master/slave transmit mode.

Otherwise it is cleared.

0 – Receive mode.

1 – Transmit mode.

MASTER The Master bit indicates that the module is

currently in master mode. It is set when a re-

quest for bus mastership succeeds. It is

cleared upon arbitration loss (BER is set) or

the recognition of a Stop Condition.

0 – Slave mode.

1 – Master mode.

NMATCH The New match bit is set when the address

byte following a Start Condition, or repeated

starts, causes a match or a global-call match.

The NMATCH bit is cleared when written with

1. Writing 0 to NMATCH is ignored. If the

ACBCTL1.INTEN bit is set, an interrupt is sent

when this bit is set.

0 – No match.

1 – Match or global-call match.

STASTR The Stall After Start bit is set by the successful

completion of an address sending (i.e., a Start

Condition sent without a bus error, or negative

acknowledge), if the ACBCTL1.STASTRE bit

is set. This bit is ignored in slave mode. When

the STASTR bit is set, it stalls the bus by pull-

ing down the SCL line, and suspends any oth-

er action on the bus (e.g., receives first byte in

master receive mode). In addition, if the

ACBCTL1.INTEN bit is set, it also sends an

interrupt to the core. Writing 1 to the STASTR

bit clears it. It is also cleared when the module

is disabled. Writing 0 to the STASTR bit has

no effect.

0 – No stall after start condition.

1 – Stall after successful start.

Table 75 ACCESS.bus Interface Registers

Name Address Description

ACBSDA FF F2A0h

ACB Serial Data

Register

ACBST FF F2A2h ACB Status Register

ACBCST FF F2A4h

ACB Control Status

Register

ACBCTL1 FF F2A6h

ACB Control

Register 1

ACBCTL2 FF F2AAh

ACB Control

Register 2

ACBCTL3 FF F2AEh

ACB Control

Register 3

ACBADDR1 FF F2A8h

ACB Own Address

Register 1

ACBADDR2 FF F2ACh

ACB Own Address

Register 2

7 0

DATA

7 6 5 4 3 2 1 0

SLVSTP

SDAST

BER

NEGACK

STASTR NMATCH

MASTER

XMIT