209 www.national.com

CP3BT26

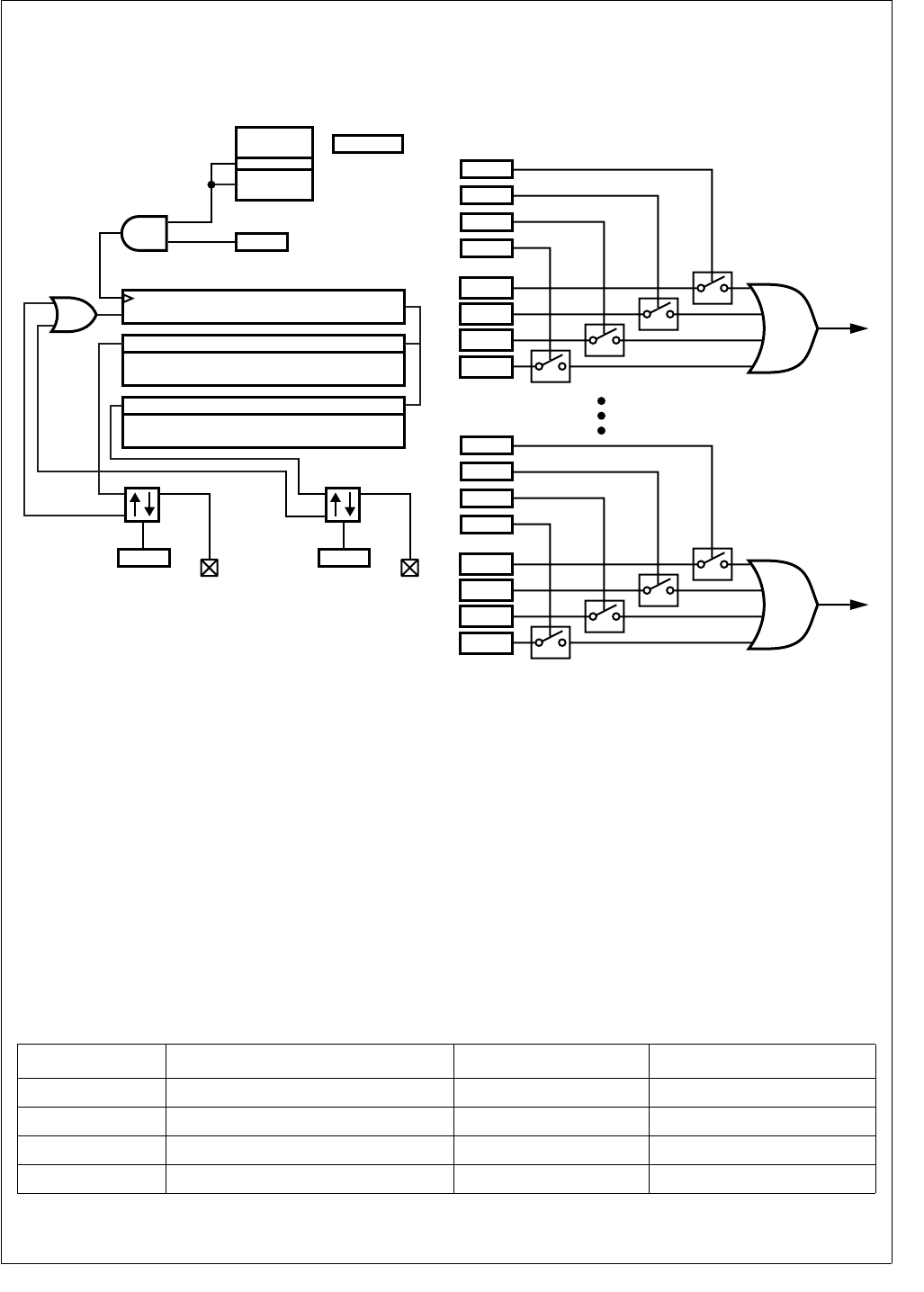

Figure 108 illustrates the configuration of a timer subsystem

while operating in capture mode. The numbering in

Figure 108 refers to timer subsystem 1 but equally applies

to the other three timer subsystems.

Figure 108. VTU Dual 16-bit Capture Mode

27.1.4 Low Power Mode

In case a timer subsystem is not used, software can place it

in a low-power mode. All clocks to a timer subsystem are

stopped and the counter and prescaler contents are frozen

once low-power mode is entered. Software may continue to

write to the MODE, INTCTL, IOxCTL, and CLKxPS regis-

ters. Write operations to the INTPND register are allowed;

but if a timer subsystem is in low-power mode, its associat-

ed interrupt pending bits cannot be cleared. Software can-

not write to the COUNTx, PERCAPx, and DTYCAPx

registers of a timer subsystem while it is in low-power mode.

All registers can be read at any time.

27.1.5 Interrupts

The VTU has a total of 16 interrupt sources, four for each of

the four timer subsystems. All interrupt sources have a

pending bit and an enable bit associated with them. All in-

terrupt pending bits are denoted IxAPD through IxDPD

where “x” relates to the specific timer subsystem. There is

one system level interrupt request for each of the four timer

subsystems.

Figure 109 illustrates the interrupt structure of the versatile

timer module.

Figure 109. VTU Interrupt Request Structure

Each of the timer pending bits - IxAPD through IxDPD - is

set by a specific hardware event depending on the mode of

operation, i.e., PWM or Capture mode. Table 80 outlines the

specific hardware events relative to the operation mode

which cause an interrupt pending bit to be set.

27.1.6 ISE Mode operation

The VTU supports breakpoint operation of the In-System-

Emulator (ISE). If FREEZE is asserted, all timer counter

clocks will be inhibited and the current value of the timer reg-

isters will be frozen; in capture mode, all further capture

events are disabled. Once FREEZE becomes inactive,

counting will resume from the previous value and the cap-

ture input events are re-enabled.

Count1[15:0]

Restart

015

15:0

C1EDG

PERCAP1[15:0]

Compare

DTYCAP1[15:0]

Compare

C1PRSC

= =

70

Prescaler

Counter

2

rst

cap

0

TMOD1=11

T1RUN

C2EDG

TIO2

2

rst

cap

0

DS092

TIO1

System

Interrupt

Request 1

I1AEN

I1BEN

I1CEN

I1DEN

I1APD

I1BPD

I1CPD

I1DPD

System

Interrupt

Request 4

I4AEN

I4BEN

I4CEN

I4DEN

I4APD

I4BPD

I4CPD

I4DPD

DS093

Table 80 VTU Interrupt Sources

Pending Flag Dual 8-bit PWM Mode 16-bit PWM Mode Capture Mode

IxAPD Low Byte Duty Cycle match Duty Cycle match Capture to PERCAPx

IxBPD Low Byte Period match Period match Capture to DTYCAPx

IxCPD High Byte Duty Cycle match N/A Counter Overflow

IxDPD High Byte Period match N/A N/A