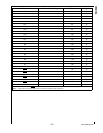

271 www.national.com

CP3BT26

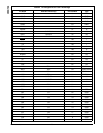

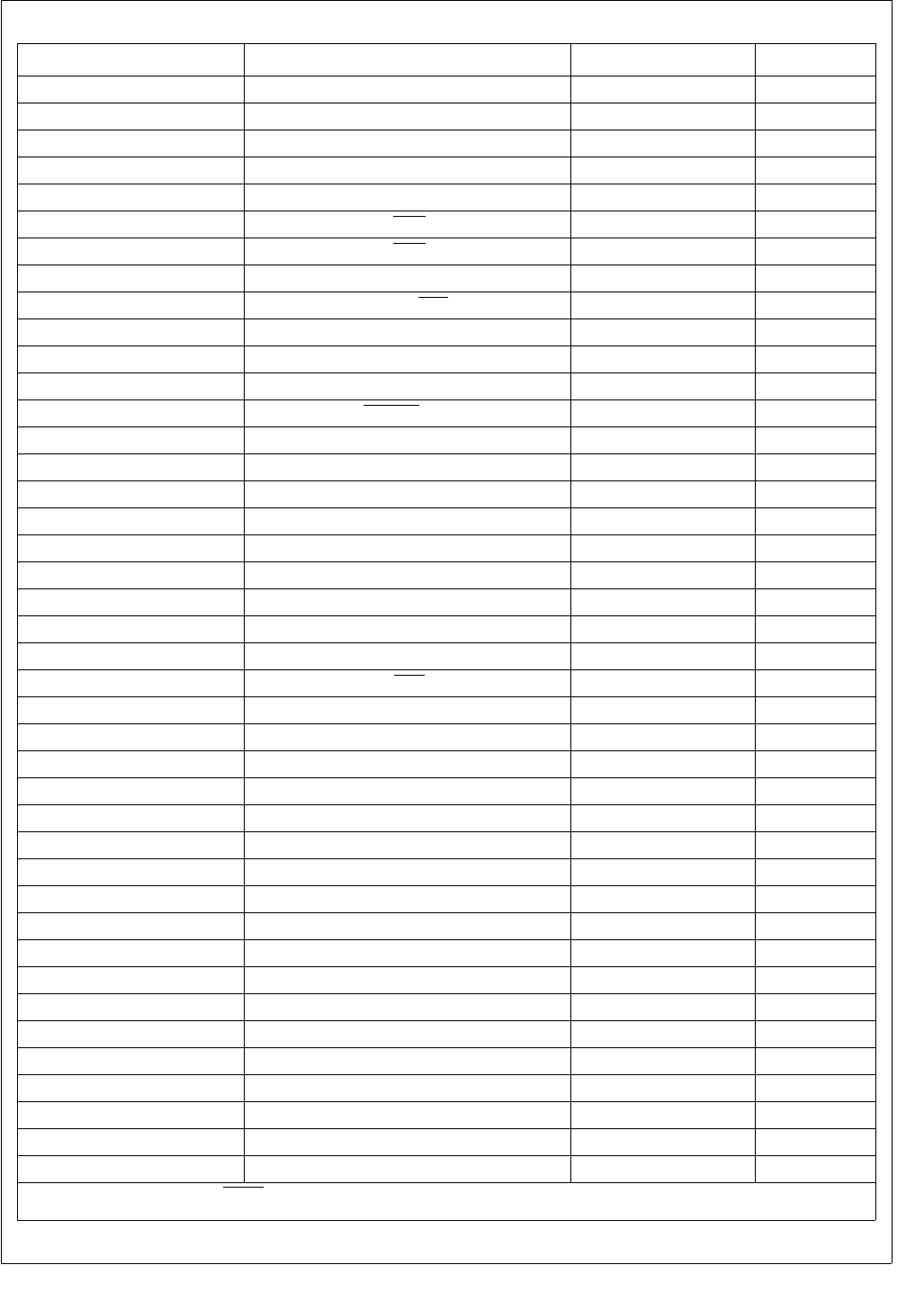

PC5 D13 5 GPIO

PC6 D14 3 GPIO

PC7 D15 2 GPIO

PE0 RXD0 87 GPIO

PE1 TXD0 83 GPIO

PE2 RTS

86 GPIO

PE3 CTS

88 GPIO

PE4 CKX/TB 40 GPIO

PE5 SRFS/NMI

120 GPIO

PF0 MSK/TIO1 111 GPIO

PF1 MDIDO/TIO2 114 GPIO

PF2 MDODI/TIO3 116 GPIO

PF3 MWCS/

TIO4 109 GPIO

PF4 SCK/TIO5 122 GPIO

PF5 SFS/TIO6 123 GPIO

PF6 STD/TIO7 125 GPIO

PF7 SRD/TIO8 126 GPIO

PG0 RFSYNC 69 GPIO

PG1 RFCE 70 GPIO

PG2 SRCLK 118 GPIO

PG3 SCLK 71 GPIO

PG4 SDAT 72 GPIO

PG5 SLE

73 GPIO

PG6 WUI10 37 GPIO

PG7 TA 41 GPIO

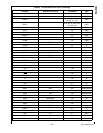

PH0 RXD1/WUI11 105 GPIO

PH1 TXD1/WUI12 46 GPIO

PH2 RXD2/WUI13 48 GPIO

PH3 TXD2/WUI14 50 GPIO

PH4 RXD3/WUI15 52 GPIO

PH5 TXD3/WUI16 54 GPIO

PH6 CANRX/WUI17 57 GPIO

PH7 CANTX 59 GPIO

PJ0 WUI18 128 GPIO

PJ1 WUI19 1 GPIO

PJ2 WUI20 38 GPIO

PJ3 WUI21 39 GPIO

PJ4 WUI22 64 GPIO

PJ5 WUI23 65 GPIO

PJ6 WUI24 66 GPIO

PJ7 ASYNC/WUI9 104 GPIO

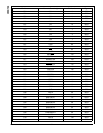

Note 1: The ENV0, ENV1, ENV2, RESET, TCK, TDI, and TMS pins each have a weak pull-up to keep the input from floating.

Note 2: These functions are always enabled, due to the direct low-impedance path to these pins.

Table 94 Pin Assignments for LQFP-128 Package

Pin Name Alternate Function(s) Pin Numbers Type