137 www.national.com

CP3BT26

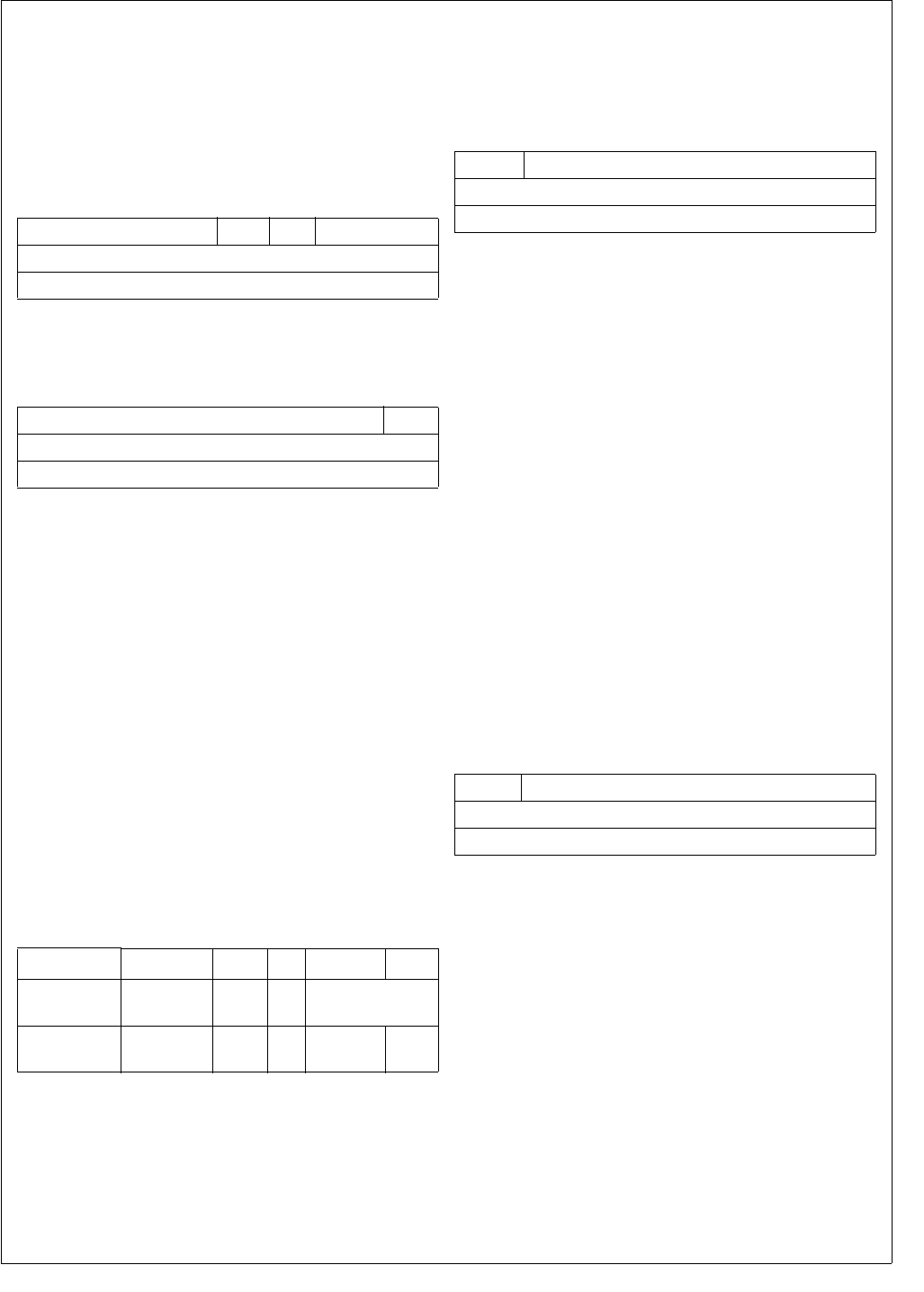

19.10.9 Basic Mask Register (BMSKB/BMSKX)

The BMSKB and BMSKX registers allow masking the buffer

14, or “don’t care” the incoming extended/standard identifier

bits, RTR/XRTR, and IDE. Throughout this document, the

two 16-bit registers BMSKB and BMSKX are referenced to

as a 32-bit register BMSK.

The following are the bits for the BMSKB register.

The following are the bits for the BMSKX register.

For all BMSKB and BMSKX register bits the following ap-

plies:

0 – The incoming identifier bit must match the correspond-

ing bit in the message buffer identifier register.

1 – Accept 1 or 0 (“don’t care”) in the incoming ID bit inde-

pendent from the corresponding bit in the message

buffer ID registers. The corresponding ID bit in the mes-

sage buffer will be overwritten by the incoming identifier

bits.

When an extended frame is received from the CAN bus, all

BMSK bits BM[28:0], IDE, RTR, and XRTR are used to

mask the incoming message. In this case, the RTR bit in the

BMSK register corresponds to the SRR bit in the message.

The XRTR bit in the BMSK register corresponds to the RTR

bit in the message.

During the reception of standard frames, only the BMSK bits

BM[28:18], RTR, and IDE are used. In this case, the

BM[28:18] bits in the BMSK register correspond to the

ID[10:0] bits in the message.

19.10.10 CAN Interrupt Enable Register (CIEN)

The CAN Interrupt Enable (CIEN) register enables the

transmit/receive interrupts of the message buffers 0 through

14 as well as the CAN Error Interrupt.

EIEN The Error Interrupt Enable bit allows the CAN

module to interrupt the CPU if any kind of

CAN receive/transmit errors are detected.

This causes any error status change in the er-

ror counter registers REC/TEC is able to gen-

erate an error interrupt.

0 – The error interrupt is disabled and no er-

ror interrupt will be generated.

1 – The error interrupt is enabled and a

change in REC/TEC will cause an inter-

rupt to be generated.

IEN The Buffer Interrupt Enable bits allow software

to enable/disable the interrupt source for the

corresponding message buffer. For example,

IEN14 controls interrupts from buffer14, and

IEN0 controls interrupts from buffer0.

0 – Buffer as interrupt source disabled.

1 – Buffer as interrupt source enabled.

19.10.11 CAN Interrupt Pending Register (CIPND)

The CIPND register indicates any CAN Receive/Transmit

Interrupt Requests caused by the message buffers 0..14

and CAN error occurrences.

EIPND The Error Interrupt Pending field indicates the

status change of TEC/REC and will execute

an error interrupt if the EIEN bit is set. Soft-

ware has the responsibility to clear the EIPND

bit using the CICLR register.

0 – CAN status is not changed.

1 – CAN status is changed.

IPND The Buffer Interrupt Pending bits are set by

the CAN module following a successful trans-

mission or reception of a message to or from

the corresponding message buffer. For exam-

ple, IPND14 corresponds to buffer14, and

IPND0 corresponds to buffer0.

0 – No interrupt pending for the correspond-

ing message buffer.

1 – Message buffer has generated an inter-

rupt.

15 5 4 3 2 0

BM[28:18] RTR IDE BM[17:15]

0

R/W

15 1 0

BM[14:0] XRTR

0

R/W

Basic Mask BM[28:18] RTR IDE BM[17:0] XRTR

Standard

Frame

ID[10:0] RTR IDE Unused

Extended

Frame

ID[28:18] SRR IDE ID[17:0] RTR

15 14 0

EIEN IEN

0

R/W

15 14 0

EIPND IPND

0

R