59 www.national.com

CP3BT26

12.6.2 Power Management Status Register (PMMSR)

The Management Status Register (PMMR) is a byte-wide,

read/write register that provides status signals for the vari-

ous clocks. The reset value of PMSR register bits 0 to 2 de-

pend on the status of the clock sources monitored by the

PMM. The upper 5 bits are clear after reset. The format of

the register is shown below.

OLC The Oscillating Low Frequency Clock bit indi-

cates whether the low-frequency oscillator is

producing a stable clock. When the low-fre-

quency oscillator is unavailable, the PMM will

not switch to Power Save, Idle, or Halt mode.

0

– Low-frequency oscillator is unstable, dis-

abled, or not oscillating.

1

– Low-frequency oscillator is available.

OMC The Oscillating Main Clock bit indicates

whether the high-frequency oscillator is pro-

ducing a stable clock. When the high-frequen-

cy oscillator is unavailable, the PMM will not

switch to Active mode.

0

– High-frequency oscillator is unstable, dis-

abled, or not oscillating.

1

– High-frequency oscillator is available.

OHC The Oscillating High Frequency (PLL) Clock

bit indicates whether the PLL is producing a

stable clock. Because the PMM tests the sta-

bility of the PLL clock to qualify power mode

state transitions, a stable clock is indicated

when the PLL is disabled. This removes the

stability of the PLL clock from the test when

the PLL is disabled. When the PLL is enabled

but unstable, the PMM will not switch to Active

mode.

0

– PLL is enabled but unstable.

1

– PLL is stable or disabled (CRCTRL.PLL-

PWD = 0).

12.7 SWITCHING BETWEEN POWER MODES

Switching from a higher to a lower power consumption

mode is performed by writing an appropriate value to the

Power Management Control/Status Register (PMMCR).

Switching from a lower power consumption mode to the Ac-

tive mode is usually triggered by a hardware interrupt.

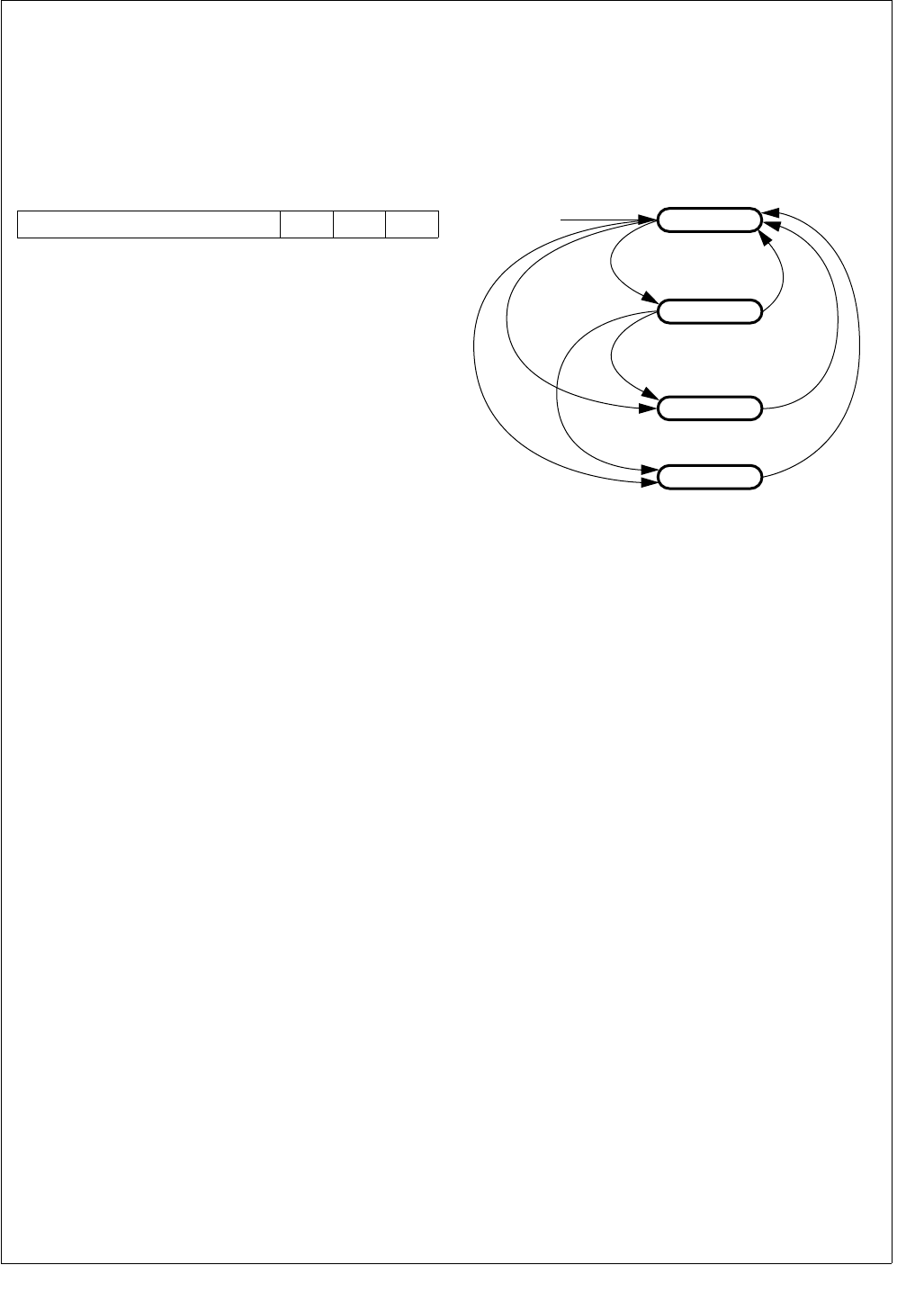

Figure 8 shows the four power consumption modes and the

events that trigger a transition from one mode to another.

Figure 8. Power Mode State Diagram

Some of the power-up transitions are based on the occur-

rence of a wake-up event. An event of this type can be either

a maskable interrupt or a non-maskable interrupt (NMI). All

of the maskable hardware wake-up events are monitored by

the Multi-Input Wake-Up (MIWU) Module, which is active in

all modes. Once a wake-up event is detected, it is latched

until an interrupt acknowledge cycle occurs or a reset is ap-

plied.

A wake-up event causes a transition to the Active mode and

restores normal clock operation, but does not start execu-

tion of the program. It is the interrupt handler associated

with the wake-up source (MIWU or NMI) that causes pro-

gram execution to resume.

12.7.1 Active Mode to Power Save Mode

A transition from Active mode to Power Save mode is per-

formed by writing a 1 to the PMMCR.PSM bit. The transition

to Power Save mode is either initiated immediately or at ex-

ecution of the next WAIT instruction, depending on the state

of the PMMCR.WBPSM bit.

For an immediate transition to Power Save mode (PM-

MCR.WBPSM = 0), the CPU continues to operate using the

low-frequency clock. The PMMCR.PSM bit becomes set

when the transition to the Power Save mode is completed.

For a transition at the next WAIT instruction (PM-

MCR.WBPSM = 1), the CPU continues to operate in Active

mode until it executes a WAIT instruction. At execution of

the WAIT instruction, the device enters the Power Save

mode, and the CPU waits for the next interrupt event. In this

case, the PMMCR.PSM bit becomes set when it is written,

even before the WAIT instruction is executed.

7 3 2 1 0

Reserved OHC OMC OLC

Reset

Active Mode

WBPSM = 1 &

HALT = 1 &

"WAIT"

WBPSM = 1 &

IDLE = 1 &

"WAIT"

WBPSM = 1 & IDLE = 1 & "WAIT"

HW Event

HW Event

HW Event

Note:

HW Event = MIWU wake-up or NMI

IDLE = 1

WBPSM = 0 & PSM = 1

or

WBPSM = 1 & PSM = 1 & "WAIT"

Power Save Mode

Idle Mode

Halt Mode

DS008