203 www.national.com

CP3BT26

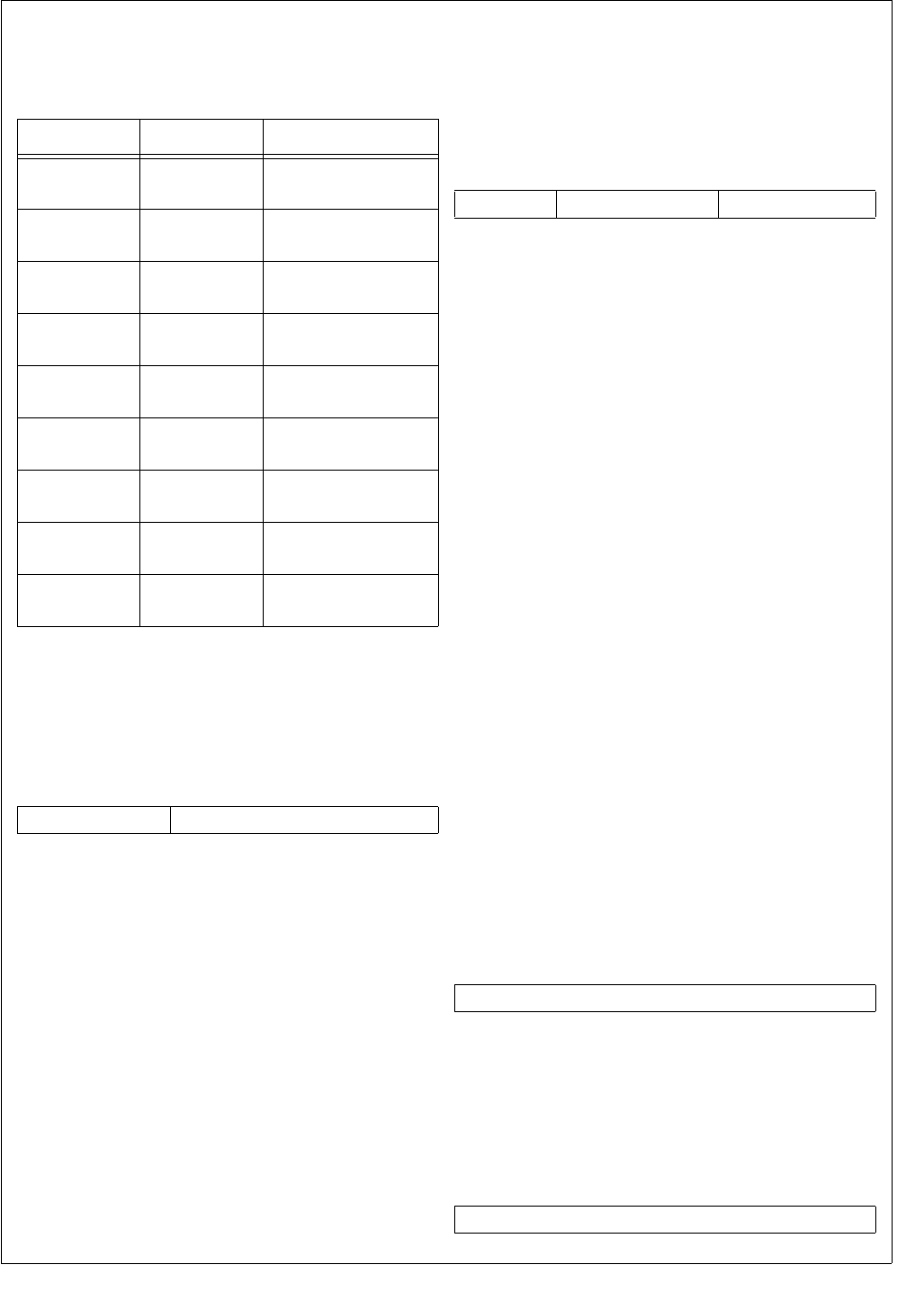

26.5 TIMER REGISTERS

Table 79 lists the CPU-accessible registers used to control

the Multi-Function Timers.

26.5.1 Clock Prescaler Register (TPRSC)

The TPRSC register is a byte-wide, read/write register that

holds the current value of the 5-bit clock prescaler (CLKPS).

This register is cleared on reset. The register format is

shown below.

CLKPS The Clock Prescaler field specifies the divisor

used to generate the Timer Clock from the

System Clock. When the timer is configured to

use the prescaled clock, the System Clock is

divided by (CLKPS + 1) to produce the timer

clock. Therefore, the System Clock divisor

can range from 1 to 32.

26.5.2 Clock Unit Control Register (TCKC)

The TCKC register is a byte-wide, read/write register that

selects the clock source for each timer/counter. Selecting

the clock source also starts the counter. This register is

cleared on reset, which disables the timer/counters. The

register format is shown below.

C1CSEL The Counter 1 Clock Select field specifies the

clock mode for Timer/Counter 1 as follows:

000 – No clock (Timer/Counter 1 stopped,

modes 1, 2, and 3 only).

001 – Prescaled System Clock.

010 – External event on TB (modes 1 and 3

only).

011 – Pulse-accumulate mode based on TB

(modes 1 and 3 only).

100 – Slow Clock.*

101 – Reserved.

110 – Reserved.

111 – Reserved.

C2CSEL The Counter 2 Clock Select field specifies the

clock mode for Timer/Counter 2 as follows:

000 – No clock (Timer/Counter 2 stopped,

modes 1, 2, and 3 only).

001 – Prescaled System Clock.

010 – External event on TB (modes 1 and 3

only).

011 – Pulse-accumulate mode based on TB

(modes 1 and 3 only).

100 – Slow Clock*

101 – Reserved.

110 – Reserved.

111 – Reserved.

* Operation of the Slow Clock is determined by the CRC-

TRL.SCLK control bit, as described in Section 11.9.1.

26.5.3 Timer/Counter 1 Register (TCNT1)

The TCNT1 register is a word-wide, read/write register that

holds the current count value for Timer/Counter 1. The reg-

ister contents are not affected by a reset and are unknown

after power-up.

26.5.4 Timer/Counter 2 Register (TCNT2)

The TCNT2 register is a word-wide, read/write register that

holds the current count value for Timer/Counter 2. The reg-

ister contents are not affected by a reset and are unknown

after power-up.

Table 79 Multi-Function Timer Registers

Name Address Description

TPRSC FF FF48h

Clock Prescaler

Register

TCKC FF FF4Ah

Clock Unit Control

Register

TCNT1 FF FF40h

Timer/Counter 1

Register

TCNT2 FF FF46h

Timer/Counter 2

Register

TCRA FF FF42h

Reload/Capture A

Register

TCRB FF FF44h

Reload/Capture B

Register

TCTRL FF FF4Ch

Timer Mode

Control Register

TICTL FF FF4Eh

Timer Interrupt

Control Register

TICLR FF FF50h

Timer Interrupt

Clear Register

7 5 4 0

Reserved CLKPS

7 6 5 3 2 0

Reserved C2CSEL C1CSEL

15 0

TCNT1

15 0

TCNT2