www.national.com 208

CP3BT26

The two I/O pins associated with a timer subsystem function

as independent PWM outputs in the dual 8-bit PWM mode.

If a PWM timer is stopped using its associated

MODE.TxRUN bit the following actions result:

The associated TIOx pin will return to its default value as

defined by the IOxCTL.PxPOL bit.

The counter will stop and will retain its last value.

Any pending updates of the PERCAPx and DTYCAPx

register will be completed.

The prescaler counter will be stopped and reset if both

MODE.TxRUN bits are cleared.

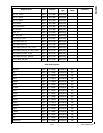

Figure 106 illustrates the configuration of a timer subsystem

while operating in dual 8-bit PWM mode. The numbering in

Figure 106 refers to timer subsystem 1 but equally applies

to the other three timer subsystems.

Figure 106. VTU Dual 8-Bit PWM Mode

27.1.2 16-Bit PWM Mode

Each of the four timer subsystems may be independently

configured to provide a single 16-bit PWM channel. In this

case the lower and upper bytes of the counter are concate-

nated to form a single 16-bit counter.

Operation in 16-bit PWM mode is conceptually identical to

the dual 8-bit PWM operation as outlined under Dual 8-bit

PWM Mode on page 207. The 16-bit timer may be started

or stopped with the lower MODE.TxRUN bit, i.e. T1RUN for

timer subsystem 1.

The two TIOx outputs associated with a timer subsystem

can be used to produce either two identical PWM wave-

forms or two PWM waveforms of opposite polarities. This

can be accomplished by setting the two PxPOL bits of the

respective timer subsystem to either identical or opposite

values.

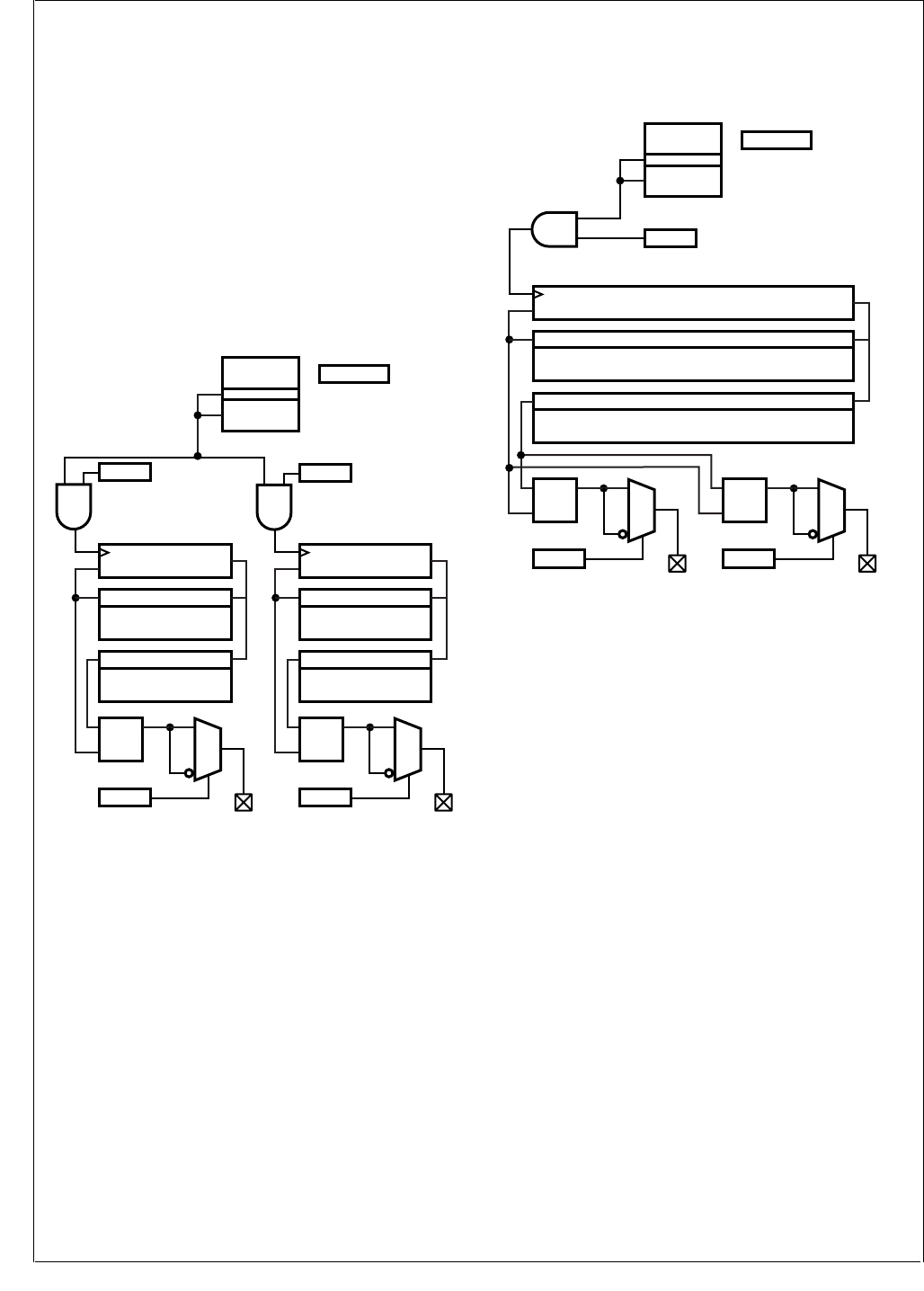

Figure 107 illustrates the configuration of a timer subsystem

while operating in 16-bit PWM mode. The numbering in

Figure 107 refers to timer subsystem 1 but equally applies

to the other three timer subsystems.

Figure 107. VTU 16-bit PWM Mode

27.1.3 Dual 16-Bit Capture Mode

In addition to the two PWM modes, each timer subsystem

may be configured to operate in an input capture mode

which provides two 16-bit capture channels. The input cap-

ture mode can be used to precisely measure the period and

duty cycle of external signals.

In capture mode the counter COUNTx operates as a 16-bit

up-counter while the two TIOx pins associated with a timer

subsystem operate as capture inputs. A capture event on

the TIOx pins causes the contents of the counter register

(COUNTx) to be copied to the PERCAPx or DTYCAPx reg-

isters respectively.

Starting the counter is identical to the 16-bit PWM mode, i.e.

setting the lower of the two MODE.TxRUN bits will start the

counter and the clock prescaler. In addition, the capture

event inputs are enabled once the MODE.TxRUN bit is set.

The TIOx capture inputs can be independently configured to

detect a capture event on either a positive transition, a neg-

ative transition or both a positive and a negative transition.

In addition, any capture event may be used to reset the

counter COUNTx and the clock prescaler counter. This

avoids the need for software to keep track of timer overflow

conditions and greatly simplifies the direct frequency and

duty cycle measurement of an external signal.

COUNT1[15:8]

Res

015

[15:8]

P2POL

TIO2

PERCAP1[15:8]

Compare

DTYCAP1[15:8]

Compare

RQ

S

C1PRSC

= =

70

Prescaler

Counter

COUNT1[7:0]

Res

07

[7:0]

P1POL

TIO1

PERCAP1[7:0]

Compare

DTYCAP1[7:0]

Compare

RQ

S

T1RUN

TMOD1 = 01

T2RUN

DS090

Count1[15:0]

Restart

015

[15:0]

P2POL

TIO2

PERCAP1[15:0]

Compare

DTYCAP1[15:0]

Compare

RQ

S

C1PRSC

= =

70

Prescaler

Counter

P1POL

TIO1

RQ

S

TMOD1 = 10

T1RUN

DS091