www.national.com 88

CP3BT26

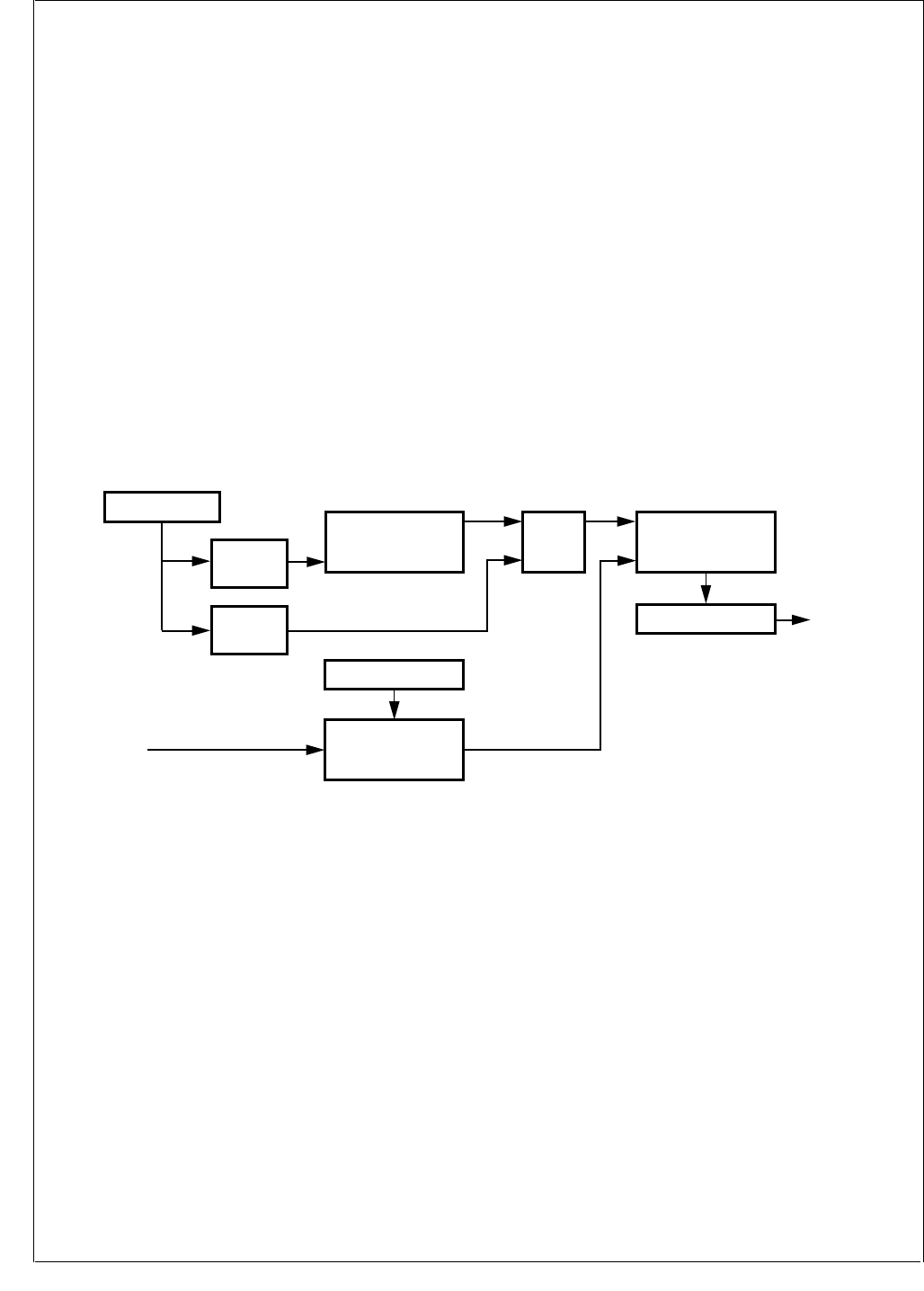

17.0 Random Number Generator (RNG)

The RNG unit is a hardware “true random” number genera-

tor. When enabled, this unit provides up to 800 random bits

per second. The bits are available for reading from a 16-bit

register.

The RNG unit includes two oscillators which operate inde-

pendently of the System Clock:

Fast Oscillator—a 24 MHz oscillator which drives a lin-

ear feedback shift register (LFSR).

Slow Oscillator—an unstable oscillator which drives a

flip-flop for sampling the pseudorandom bitstream from

the LFSR. This oscillator operates at approximately 115

kHz, but it does not have a fixed frequency.

By sampling the pseudorandom bitstream at random inter-

vals, a random bitstream is synthesized. This bitstream is

clocked into a 16-bit shift register. A programmable clock di-

vider generates the clock signal for the shift register from the

System Clock.

When a new 16-bit word of random data is available, it is

loaded into the RNGD register. If enabled, an interrupt re-

quest (IRQ3) is asserted when the word is available for

reading. When software reads the RNGD register, the reg-

ister is cleared and the interrupt request is deasserted.

The RNGCST register provides control and status bits for

the RNG module:

RNG Enable—enables or disables the RNG oscillators.

Interrupt Mask—enables or disables the interrupt when

a new word of random data becomes available.

Data Valid—indicates whether a new word is available.

17.1 FREEZE

The RNG module provides support for an In-System Emu-

lator by means of a special FREEZE input. When FREEZE

is asserted, the automatic clear-on-read function of the

RNDGD register is disabled.

Figure 28. RNG Module Block Diagram

DS185

Sample Strobe

Divider

RNGDIVH/RNGDIVL

RNGD

System

Clock

31-Bit LFSR

Clock

Sample

Flip-Flop

Clock

D

16-Bit Shift Register

RNGCST

Slow Osc.

(~115 kHz)

(Unstable)

Fast Osc.

(~24 MHz)

Clock

DQQ

Enable

System

Bus