247 www.national.com

CP3BT26

30.6 OUTPUT SIGNAL LEVELS

All output signals are powered by the digital supply (VCC).

Table 83 summarizes the states of the output signals during

the reset state (when VCC power exists in the reset state)

and during the Power Save mode.

The RESET

and NMI input pins are active during the Power

Save mode. In order to guarantee that the Power Save cur-

rent not exceed 1 mA, these inputs must be driven to a volt-

age lower than 0.5V or higher than VCC - 0.5V. An input

voltage between 0.5V and (VCC - 0.5V) may result in power

consumption exceeding 1 mA.

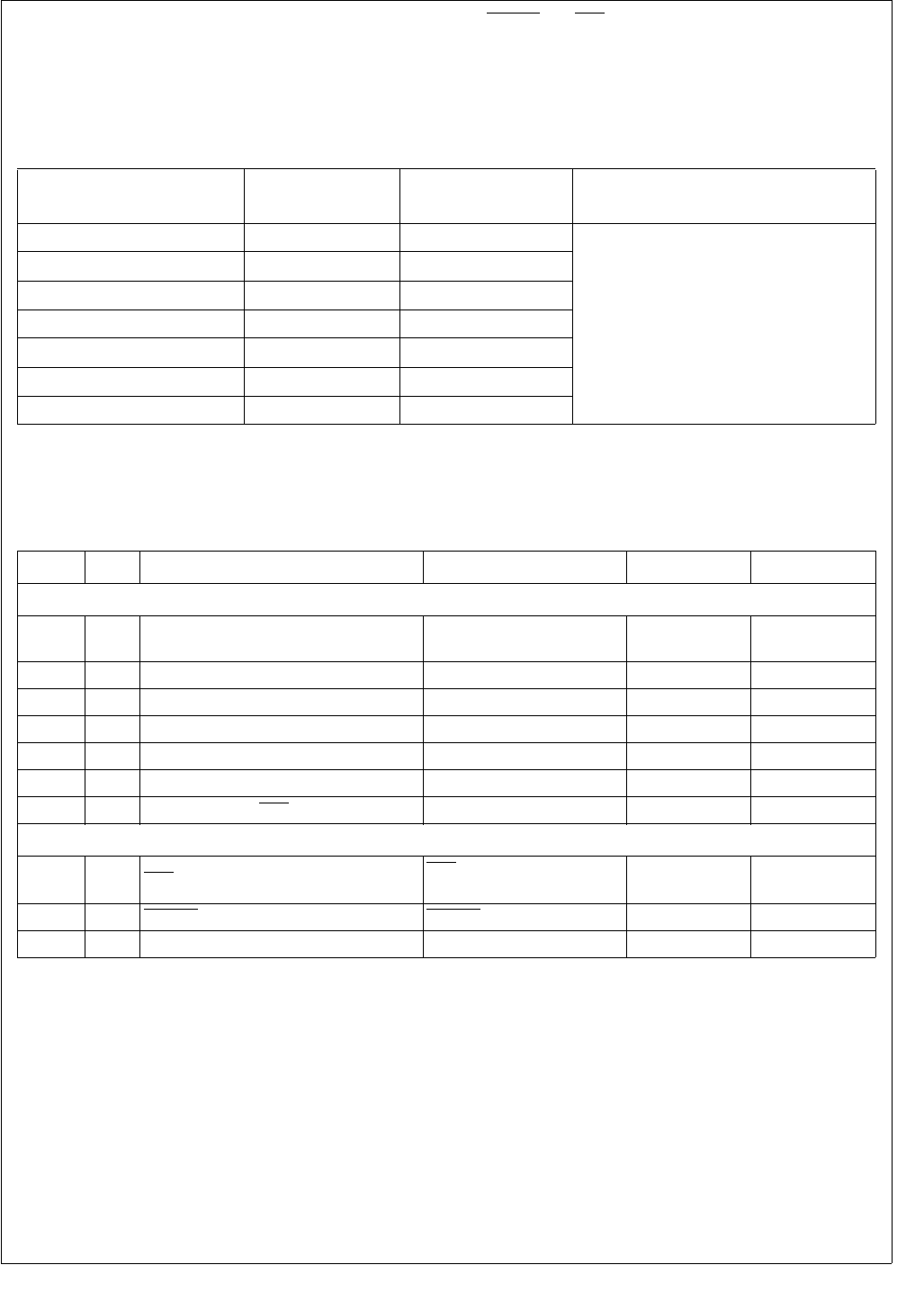

30.7 CLOCK AND RESET TIMING

Table 83 Output Pins During Reset and Power-Save

Signals on a Pin

Reset State

(with Vcc)

Power Save Mode Comments

PB7:0 TRI-STATE Previous state I/O ports will maintain their values when

entering power-save mode

PC7:0 TRI-STATE Previous state

PE5:0 TRI-STATE Previous state

PF7:0 TRI-STATE Previous state

PG7:0 TRI-STATE Previous state

PH7:0 TRI-STATE Previous state

PJ7:0 TRI-STATE Previous state

Table 84 Clock and Reset Signals

Symbol

Figure

Description Reference Min (ns) Max (ns)

Clock Input Signals

t

X1p

110 X1 period

Rising Edge (RE) on X1 to

next RE on X1

83.33 83.33

t

X1h

110 X1 high time, external clock At 2V level (Both Edges) (0.5 Tclk) - 5

t

X1l

110 X1 low time, external clock At 0.8V level (Both Edges) (0.5 Tclk) - 5

t

X2p

110 X2 period

a

RE on X2 to next RE on X2 10,000

t

X2h

110 X2 high time, external clock At 2V level (both edges) (0.5 Tclk) - 500

t

X2l

110 X2 low time, external clock At 0.8V level (both edges) (0.5 Tclk) - 500

t

IH

111 Input hold time (NMI, RXD1, RXD2) After RE on CLK 0

Reset and NMI Input Signals

t

IW

111 NMI Pulse Width

NMI

Falling Edge (FE) to

RE

20

t

RST

112 RESET Pulse Width RESET FE to RE 100

t

R

112 Vcc Rise Time 0.1 Vcc to 0.9 Vcc

a. Only when operating with an external square wave on X2CKI; otherwise a 32 kHz crystal network must be

used between X2CKI and X2CKO. If Slow Clock is internally generated from Main Clock, it may not exceed

this given limit.