177 www.national.com

CP3BT26

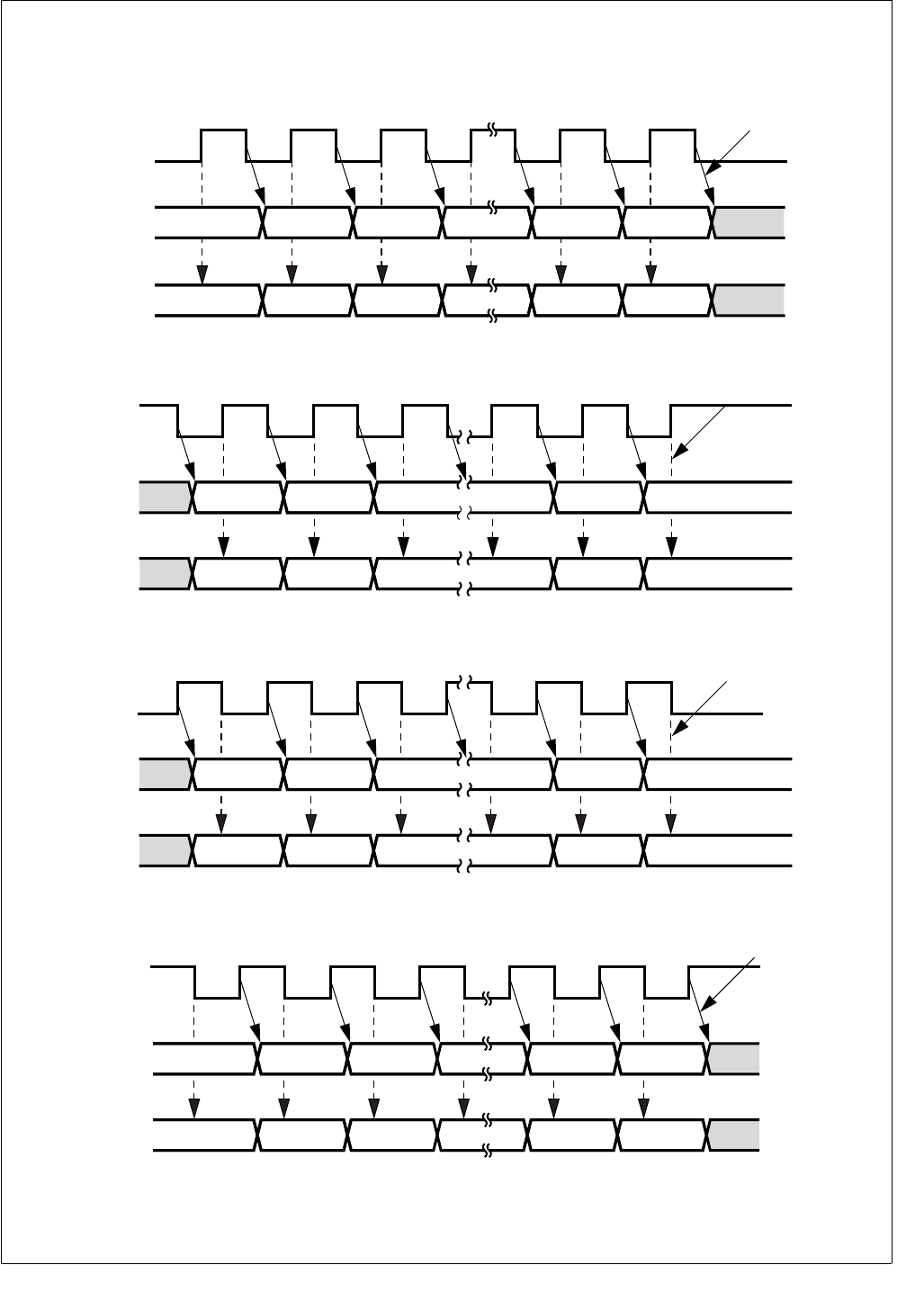

23.2 MASTER MODE

In Master mode, the MSK pin is an output for the shift clock,

MSK. When data is written to the MWDAT register, eight or

sixteen MSK clocks, depending on the mode selected, are

generated to shift the 8 or 16 bits of data, and then MSK

goes idle again. The MSK idle state can be either high or

low, depending on the SCIDL bit.

Figure 85. Normal Mode (SCIDL = 0)

Figure 86. Normal Mode (SCIDL = 1)

Figure 87. Alternate Mode (SCIDL = 0)

Figure 88. Alternate Mode (SCIDL = 1)

Bit 0

(LSB)

Bit 1MSB - 2MSB - 1

MSK

End of Transfer

Sample

Point

Shift

Out

Data Out

MSB

Bit 0

(LSB)

Bit 1MSB - 2MSB - 1

Data In

MSB

DS069

Bit 0

(LSB)

Bit 1MSB - 2MSB - 1

MSK

End of Transfer

Data Out

MSB

Bit 0

(LSB)

Bit 1MSB - 2MSB - 1

Data In

MSB

Sample

Point

Shift

Out

DS070

Bit 0

(LSB)

Bit 1MSB - 2MSB - 1

MSK

End of Transfer

Data Out

MSB

Bit 0

(LSB)

Bit 1MSB - 2MSB - 1

Data In

MSB

Sample

Point

Shift

Out

DS071

Bit 0

(LSB)

Bit 1MSB - 2MSB - 1

MSK

End of Transfer

Sample

Point

Shift

Out

Data Out

MSB

Bit 0

(LSB)

Bit 1MSB - 2MSB - 1

Data In

MSB

DS072