Instruction Set

3-69

RISC 16−Bit CPU

SXT Extend Sign

Syntax SXT dst

Operation Bit 7 −> Bit 8 ......... Bit 15

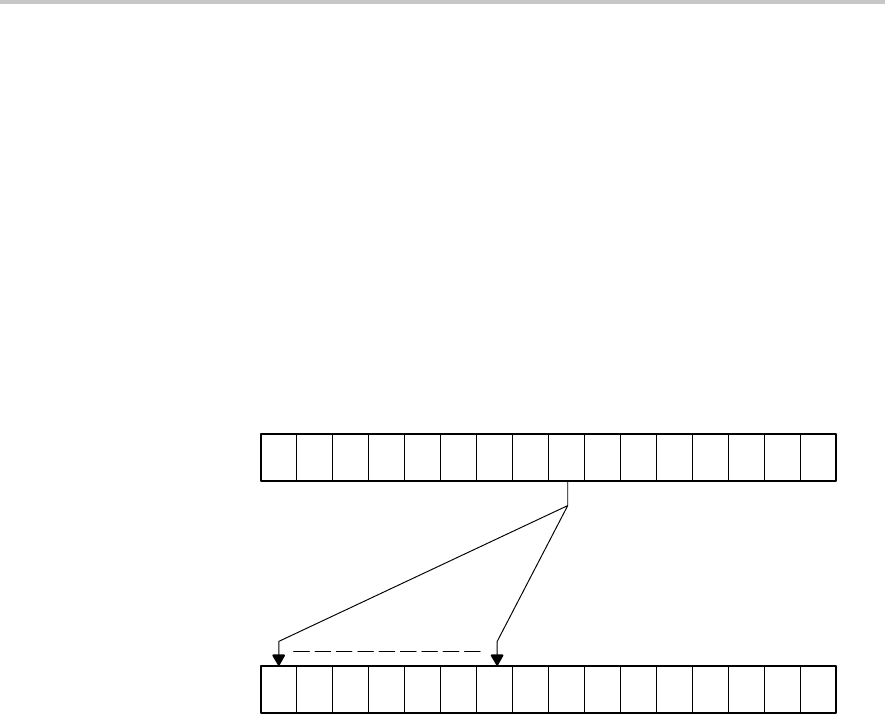

Description The sign of the low byte is extended into the high byte as shown in Figure 3−19.

Status Bits N: Set if result is negative, reset if positive

Z: Set if result is zero, reset otherwise

C: Set if result is not zero, reset otherwise (.NOT. Zero)

V: Reset

Mode Bits OSCOFF, CPUOFF, and GIE are not affected.

Figure 3−19. Destination Operand Sign Extension

15 8 7 0

Example R7 is loaded with the P1IN value. The operation of the sign-extend instruction

expands bit 8 to bit 15 with the value of bit 7.

R7 is then added to R6.

MOV.B &P1IN,R7 ; P1IN = 080h: . . . . . . . . 1000 0000

SXT R7 ; R7 = 0FF80h: 1111 1111 1000 0000