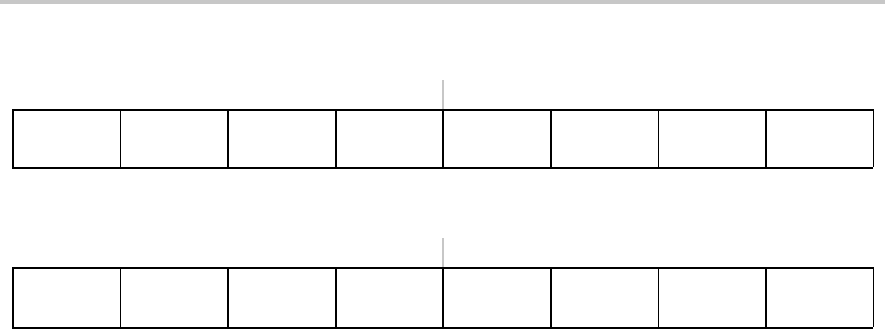

8-20

DMACTL1, DMA Control Register 1

15 14 13 12 11 10 9 8

0

0 0 0 0 0 0 0

r0 r0 r0 r0 r0 r0 r0 r0

76543210

0 0 0 0 0

DMA

ONFETCH

ROUND

ROBIN

ENNMI

r0 r0 r0 r0 r0 rw−(0) rw−(0) rw−(0)

Reserved

Bits

15−3

Reserved. Read only. Always read as 0.

DMA

ONFETCH

Bit 2 DMA on fetch

0 The DMA transfer occurs immediately

1 The DMA transfer occurs on next instruction fetch after the trigger

ROUND

ROBIN

Bit 1 Round robin. This bit enables the round-robin DMA channel priorities.

0 DMA channel priority is DMA0 − DMA1 − DMA2

1 DMA channel priority changes with each transfer

ENNMI

Bit 0 Enable NMI. This bit enables the interruption of a DMA transfer by an NMI

interrupt. When an NMI interrupts a DMA transfer, the current transfer is

completed normally, further transfers are stopped, and DMAABORT is set.

0 NMI interrupt does not interrupt DMA transfer

1 NMI interrupt interrupts a DMA transfer