DAC12 Registers

23-12 DAC12

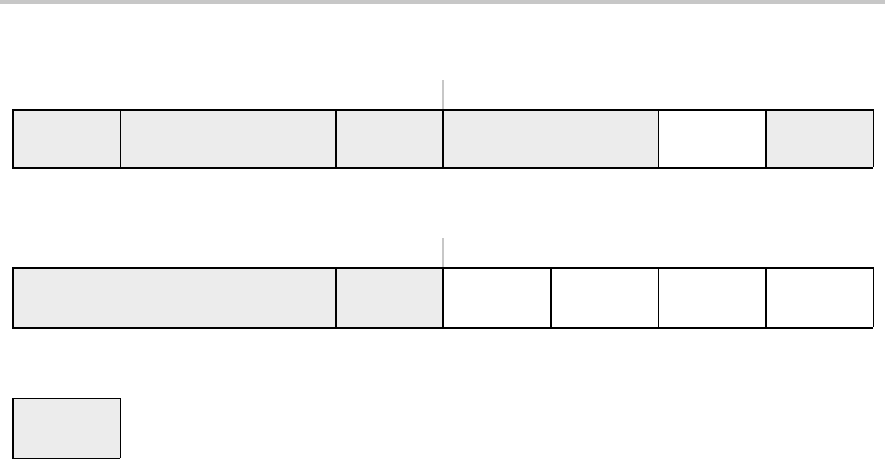

DAC12_xCTL, DAC12 Control Register

15 14 13 12 11 10 9 8

DAC12OPS DAC12SREFx DAC12RES DAC12LSELx

DAC12

CALON

DAC12IR

rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0)

76543210

DAC12AMPx DAC12DF DAC12IE DAC12IFG DAC12ENC

DAC12

GRP

rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0)

Modifiable only when DAC12ENC = 0

DAC12OPS

Bit 15 DAC12 output select for MSP430FG43x and MSP430x42x0 devices. This

bit is reserved on all other devices.

MSP430FG43x Devices:

0 DAC12_0 output on P6.6, DAC12_1 output on P6.7

1 DAC12_0 output on VeREF+, DAC12_1 output on P5.1

MSP430x42x0 Devices:

0 DAC12_0 output not available external to the device

1 DAC12_0 output available internally and externally.

DAC12

SREFx

Bits

14-13

DAC12 select reference voltage

MSP430FG43x Devices:

00 V

REF+

01 V

REF+

10 Ve

REF+

11 Ve

REF+

MSP430x42x0 Devices:

00 AV

CC

01 AV

CC

10 V

REF

(internal from SD16_A or external)

11 V

REF

(internal from SD16_A or external)

DAC12

RES

Bit 12 DAC12 resolution select

0 12-bit resolution

1 8-bit resolution

DAC12

LSELx

Bits

11-10

DAC12 load select. Selects the load trigger for the DAC12 latch. DAC12ENC

must be set for the DAC to update, except when DAC12LSELx = 0.

00 DAC12 latch loads when DAC12_xDAT written (DAC12ENC is ignored)

01 DAC12 latch loads when DAC12_xDAT written, or, when grouped,

when all DAC12_xDAT registers in the group have been written.

10 Rising edge of Timer_A.OUT1 (TA1)

11 Rising edge of Timer_B.OUT2 (TB2)