System Reset and Initialization

2-2 System Resets, Interrupts, and Operating Modes

2.1 System Reset and Initialization

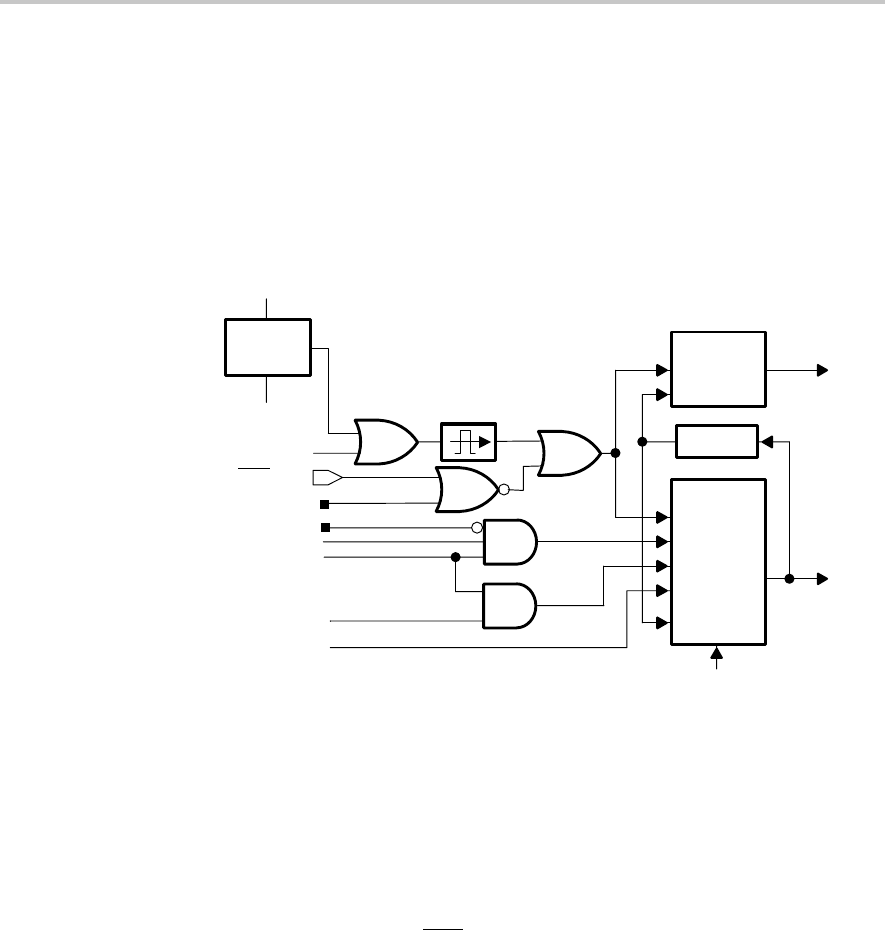

The system reset circuitry shown in Figure 2−1 sources both a power-on reset

(POR) and a power-up clear (PUC) signal. Different events trigger these reset

signals and different initial conditions exist depending on which signal was

generated.

Figure 2−1. Power-On Reset and Power-Up Clear Schematic

POR

Latch

S

R

PUC

Latch

S

R

Resetwd1

Resetwd2

S

S

Delay

RST/NMI

WDTNMI

†

WDTSSEL

†

WDTQn

†

WDTIFG

†

EQU

†

MCLK

POR

PUC

S

(from flash module)

KEYV

SVS_POR

0 V

V

CC

0 V

Brownout

Reset

† From watchdog timer peripheral module

~ 50us

A POR is a device reset. A POR is only generated by the following three

events:

- Powering up the device

- A low signal on the RST/NMI pin when configured in the reset mode

- An SVS low condition when PORON = 1.

A PUC is always generated when a POR is generated, but a POR is not

generated by a PUC. The following events trigger a PUC:

- A POR signal

- Watchdog timer expiration when in watchdog mode only

- Watchdog timer security key violation

- A Flash memory security key violation