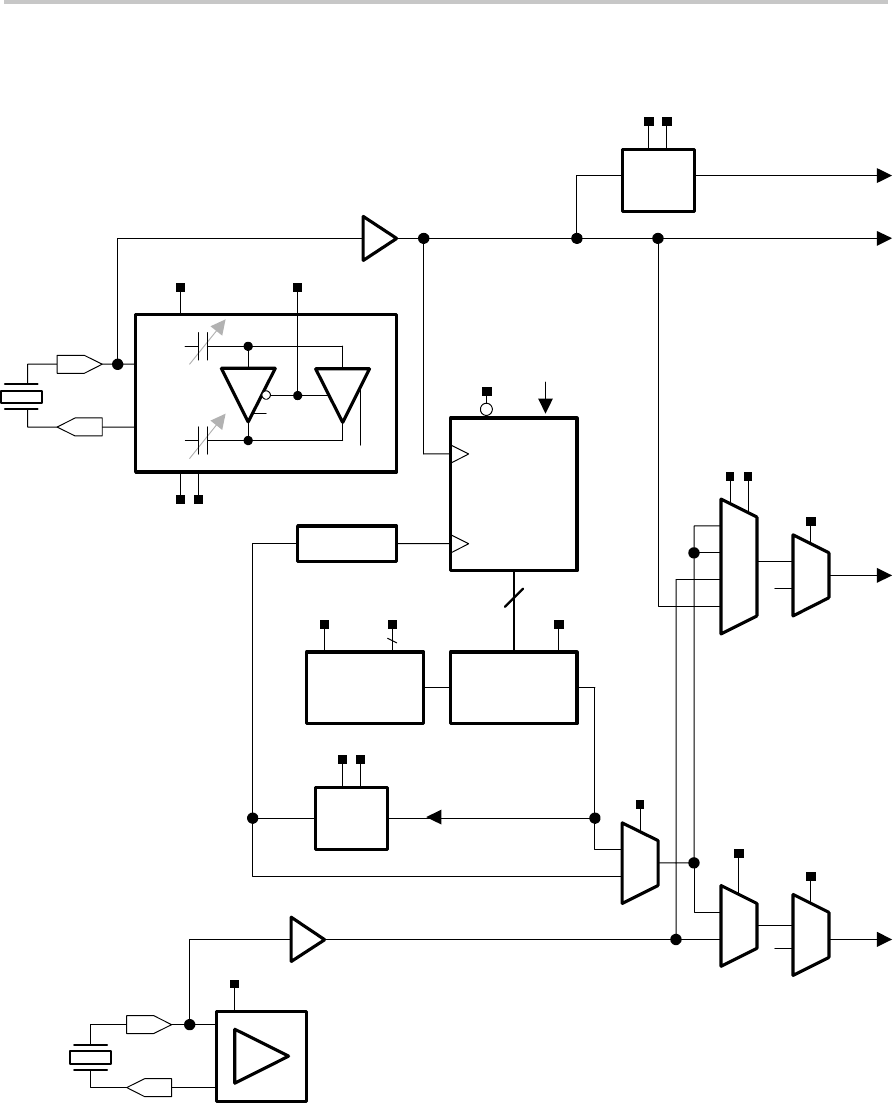

4-3FLL+ Clock Module

Figure 4−1. MSP430x44x and MSP430x43x Frequency-Locked Loop

10−bit

Frequency

Integrator

DCO

+

Modulator

DC

Generator

OSCOFF

FNxSCG1

off

SCG0

Enable

PUC

Reset

ACLK

MCLK

XTS_FLL

DCOPLUS

FLL_DIVx

FLLDx

ACLK/n

CPUOFF

XT20FF

SELS

SELMx

10

M

f

Crystal

SMCLK

SMCLKOFF

XIN

XOUT

XT2IN

XT2OUT

XT2 Oscillator

f

DCO

+

−

f

DCO/D

/(N+1)

0

1

1

0

1

0

1

0

00

01

10

11

00

01

10

11

Divider

/1/2/4/8

Divider

/1/2/4/8

4

LFXT1 Oscillator

LF

XT

0 V

LFOff

XT1Off

0 V

f

DCOCLK

XCAPxPF