Timer_B Registers

13-21Timer_B

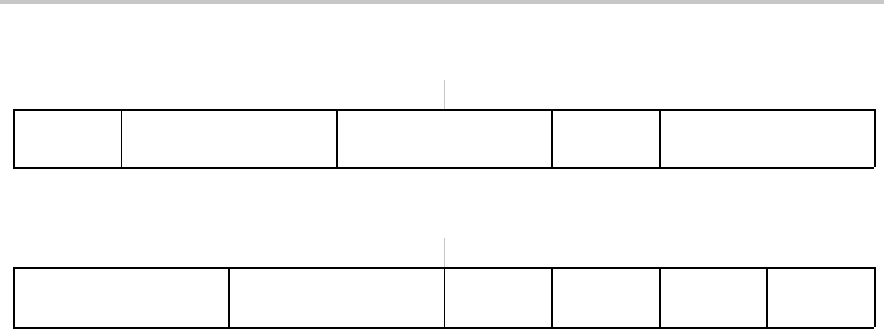

Timer_B Control Register TBCTL

15 14 13 12 11 10 9 8

Unused

TBCLGRPx CNTLx Unused TBSSELx

rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0)

76543210

IDx MCx Unused TBCLR TBIE TBIFG

rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) w−(0) rw−(0) rw−(0)

Unused

Bit 15 Unused

TBCLGRP

Bit

14-13

TBCLx group

00 Each TBCLx latch loads independently

01 TBCL1+TBCL2 (TBCCR1 CLLDx bits control the update)

TBCL3+TBCL4 (TBCCR3 CLLDx bits control the update)

TBCL5+TBCL6 (TBCCR5 CLLDx bits control the update)

TBCL0 independent

10 TBCL1+TBCL2+TBCL3 (TBCCR1 CLLDx bits control the update)

TBCL4+TBCL5+TBCL6 (TBCCR4 CLLDx bits control the update)

TBCL0 independent

11 TBCL0+TBCL1+TBCL2+TBCL3+TBCL4+TBCL5+TBCL6

(TBCCR1 CLLDx bits control the update)

CNTLx

Bits

12-11

Counter Length

00 16-bit, TBR

(max)

= 0FFFFh

01 12-bit, TBR

(max)

= 0FFFh

10 10-bit, TBR

(max)

= 03FFh

11 8-bit, TBR

(max)

= 0FFh

Unused

Bit 10 Unused

TBSSELx

Bits

9-8

Timer_B clock source select.

00 TBCLK

01 ACLK

10 SMCLK

11 Inverted TBCLK

IDx

Bits

7-6

Input divider. These bits select the divider for the input clock.

00 /1

01 /2

10 /4

11 /8

MCx

Bits

5-4

Mode control. Setting MCx = 00h when Timer_B is not in use conserves

power.

00 Stop mode: the timer is halted

01 Up mode: the timer counts up to TBCL0

10 Continuous mode: the timer counts up to the value set by TBCNTLx

11 Up/down mode: the timer counts up to TBCL0 and down to 0000h