SD16 Registers

21-19SD16

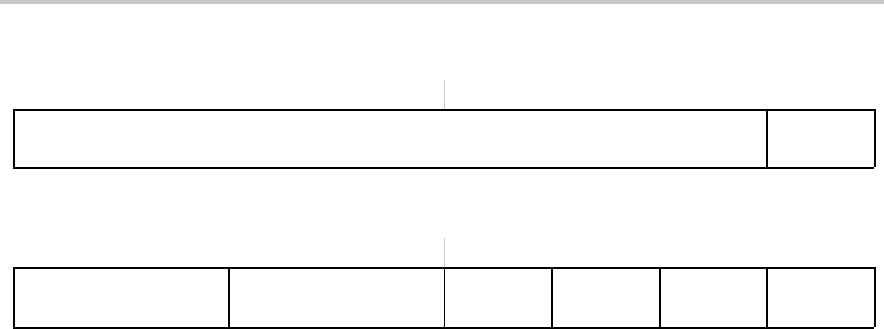

SD16CTL, SD16 Control Register

15 14 13 12 11 10 9 8

Reserved SD16LP

r0 r0 r0 r0 r0 r0 r0 rw−0

76543210

SD16DIVx SD16SSELx

SD16

VMIDON

SD16

REFON

SD16OVIE Reserved

rw−0 rw−0 rw−0 rw−0 rw−0 rw−0 rw−0 r0

Reserved

Bits

15-9

Reserved

SD16LP

Bit 8 Low power mode. This bit selects a reduced speed, reduced power mode

for the SD16.

0 Low-power mode is disabled

1 Low-power mode is enabled. The maximum clock frequency for the

SD16 is reduced.

SD16DIVx

Bits

7-6

SD16 clock divider

00 /1

01 /2

10 /4

11 /8

SD16SSELx

Bits

5-4

SD16 clock source select

00 MCLK

01 SMCLK

10 ACLK

11 External TACLK

SD16

VMIDON

Bit 3 V

MID

buffer on

0Off

1On

SD16

REFON

Bit 2 Reference generator on

0 Reference off

1 Reference on

SD16OVIE

Bit 1 SD16 overflow interrupt enable. The GIE bit must also be set to enable the

interrupt.

0 Overflow interrupt disabled

1 Overflow interrupt enabled

Reserved

Bit 0 Reserved