Instruction Set

3-18 RISC 16-Bit CPU

3.4.1 Double-Operand (Format I) Instructions

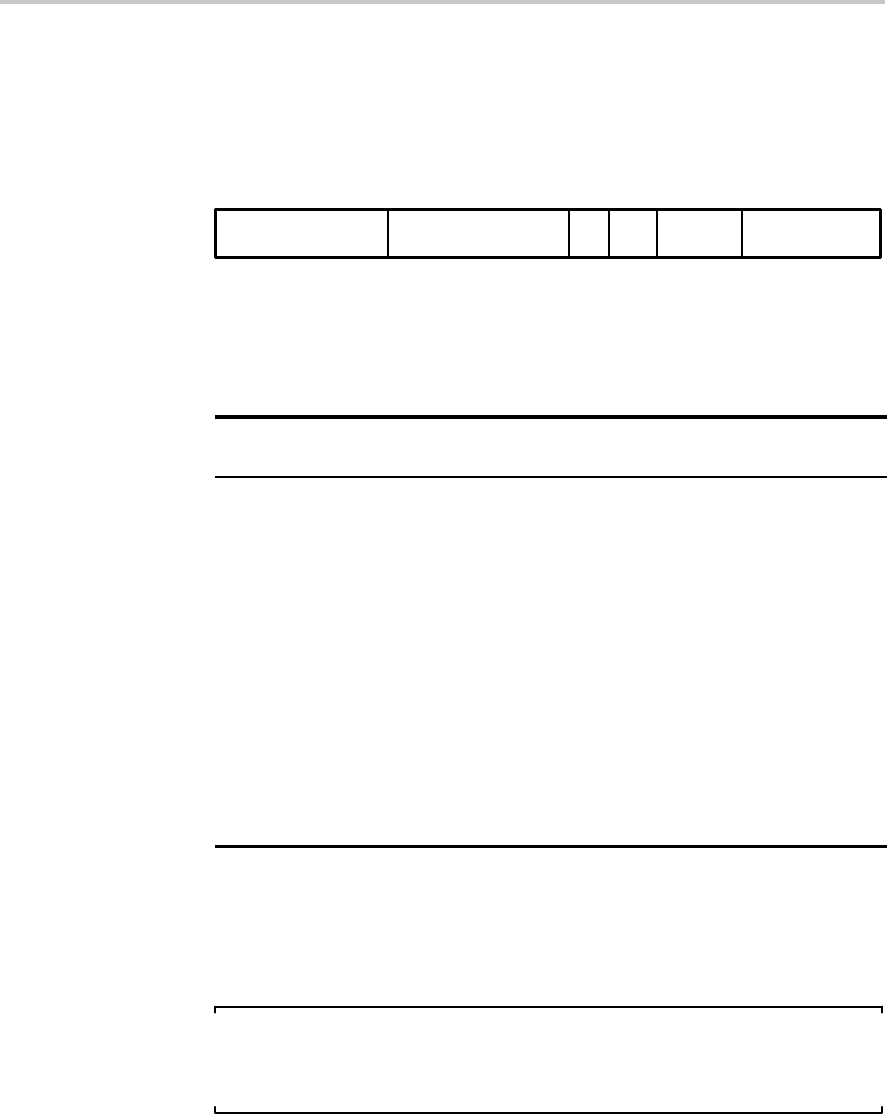

Figure 3−9 illustrates the double-operand instruction format.

Figure 3−9. Double Operand Instruction Format

B/W D-Reg

15 0

Op-code

AdS-Reg

8714 13 12 11 10 9 6 5 4 3 2 1

As

Table 3−11 lists and describes the double operand instructions.

Table 3−11.Double Operand Instructions

Mnemonic S-Reg,

Operation Status Bits

D-Reg

VNZC

MOV(.B)

src,dst src → dst − − − −

ADD(.B) src,dst src + dst → dst ****

ADDC(.B) src,dst src + dst + C → dst ****

SUB(.B) src,dst dst + .not.src + 1 → dst ****

SUBC(.B) src,dst dst + .not.src + C → dst ****

CMP(.B) src,dst dst − src ****

DADD(.B) src,dst src + dst + C → dst (decimally) * * * *

BIT(.B) src,dst src .and. dst 0 * * *

BIC(.B) src,dst .not.src .and. dst → dst −−−−

BIS(.B) src,dst src .or. dst → dst −−−−

XOR(.B) src,dst src .xor. dst → dst ****

AND(.B)

src,dst src .and. dst → dst 0 * * *

* The status bit is affected

− The status bit is not affected

0 The status bit is cleared

1 The status bit is set

Note: Instructions CMP and SUB

The instructions CMP and SUB are identical except for the storage of the

result. The same is true for the BIT and AND instructions.