Scan IF Registers

24-48 Scan IF

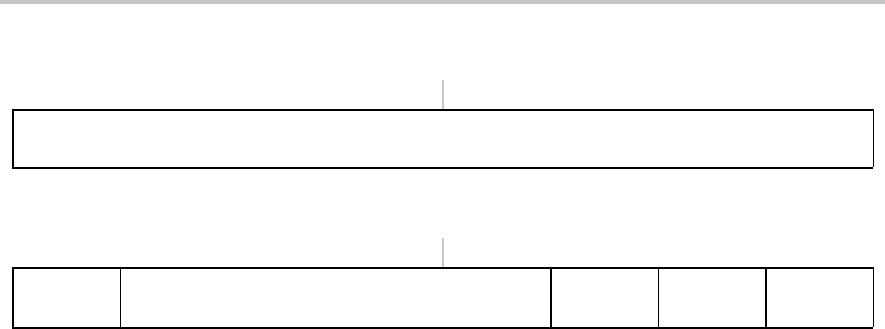

SIFCTL5, Scan IF Control Register 5

15 14 13 12 11 10 9 8

SIFCNT3x

rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0)

76543210

SIFTSMRP SIFCLFQx SIFFNOM

SIFCLKG

ON

SIFCLKEN

rw−(0) rw−(1) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0)

SIFCNT3x

Bits

15-8

Internal oscillator counter. SIFCNT3 counts internal oscillator clock cycles

during one ACLK period when SIFFNOM = 0 or during four ACLK periods

when SIFFNOM = 1 after SIFCLKGON and SIFCLKEN are both set

SIFTSMRP

Bit 7 TSM repeat mode

0 Each TSM sequence is triggered by the ACLK divider controlled with the

SIFDIV3Ax and SIFDIV3Bx bits.

1 Each TSM sequence is immediately started at the end of the previous

sequence.

SIFCLKFQx

Bits

6-3

Internal oscillator frequency adjust. These bits are used to adjust the internal

oscillator frequency. Each increase or decrease of the SIFCLKFQx bits

increases or decreases the internal oscillator frequency by approximately 5%.

0000 Minimum frequency

:

1000 Nominal frequency

:

1111 Maximum frequency

SIFFNOM

Bit 2 Internal oscillator nominal frequency

0 4 MHz

1 1 MHz

SIFCLKG

ON

Bit 1 Internal oscillator control. When SIFCLKGON = 1 and SIFCLKEN = 1, the

internal oscillator calibration is started. SIFCLKGON is not used when

SIFCLKEN = 0.

0 No internal oscillator calibration is started.

1 The internal oscillator calibration is started when SIFCLKEN = 1.

SIFCLKEN

Bit 0 Internal oscillator enable. This bit selects the high frequency clock source for

the TSM.

0 TSM high frequency clock source is SMCLK.

1 TSM high frequency clock source is the Scan IF internal oscillator.