SD16 Registers

21-20 SD16

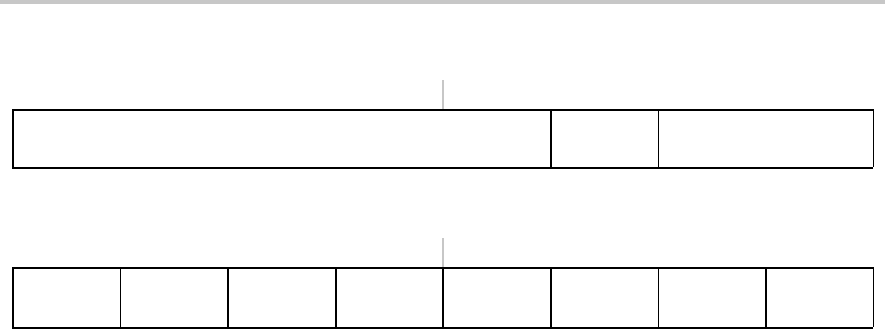

SD16CCTLx, SD16 Channel x Control Register

15 14 13 12 11 10 9 8

Reserved SD16SNGL SD16OSRx

r0 r0 r0 r0 r0 rw−0 rw−0 rw−0

76543210

SD16

LSBTOG

SD16

LSBACC

SD16

OVIFG

SD16DF SD16IE SD16IFG SD16SC SD16GRP

rw−0 rw−0 rw−0 rw−0 rw−0 rw−0 rw−0 r(w)−0

Reserved

Bits

15-11

Reserved

SD16SNGL

Bit 10 Single conversion mode select

0 Continuous conversion mode

1 Single conversion mode

SD16OSRx

Bits

9-8

Oversampling ratio

00 256

01 128

10 64

11 32

SD16

LSBTOG

Bit 7 LSB toggle. This bit, when set, causes SD16LSBACC to toggle each time

the SD16MEMx register is read.

0 SD16LSBACC does not toggle with each SD16MEMx read

1 SD16LSBACC toggles with each SD16MEMx read

SD16

LSBACC

Bit 6 LSB access. This bit allows access to the upper or lower 16-bits of the

SD16 conversion result.

0 SD16MEMx contains the most significant 16-bits of the conversion.

1 SD16MEMx contains the least significant 16-bits of the conversion.

SD16OVIFG

Bit 5 SD16 overflow interrupt flag

0 No overflow interrupt pending

1 Overflow interrupt pending

SD16DF

Bit 4 SD16 data format

0 Offset binary

12’s complement

SD16IE

Bit 3 SD16 interrupt enable

0 Disabled

1 Enabled