USART Operation: SPI Mode

15-7USART Peripheral Interface, SPI Mode

15.2.4 SPI Enable

The SPI transmit/receive enable bit USPIEx enables or disables the USART

in SPI mode. When USPIEx = 0, the USART stops operation after the current

transfer completes, or immediately if no operation is active. A PUC or set

SWRST bit disables the USART immediately and any active transfer is

terminated.

Transmit Enable

When USPIEx = 0, any further write to UxTXBUF does not transmit. Data

written to UxTXBUF will begin to transmit when USPIEx = 1 and the BRCLK

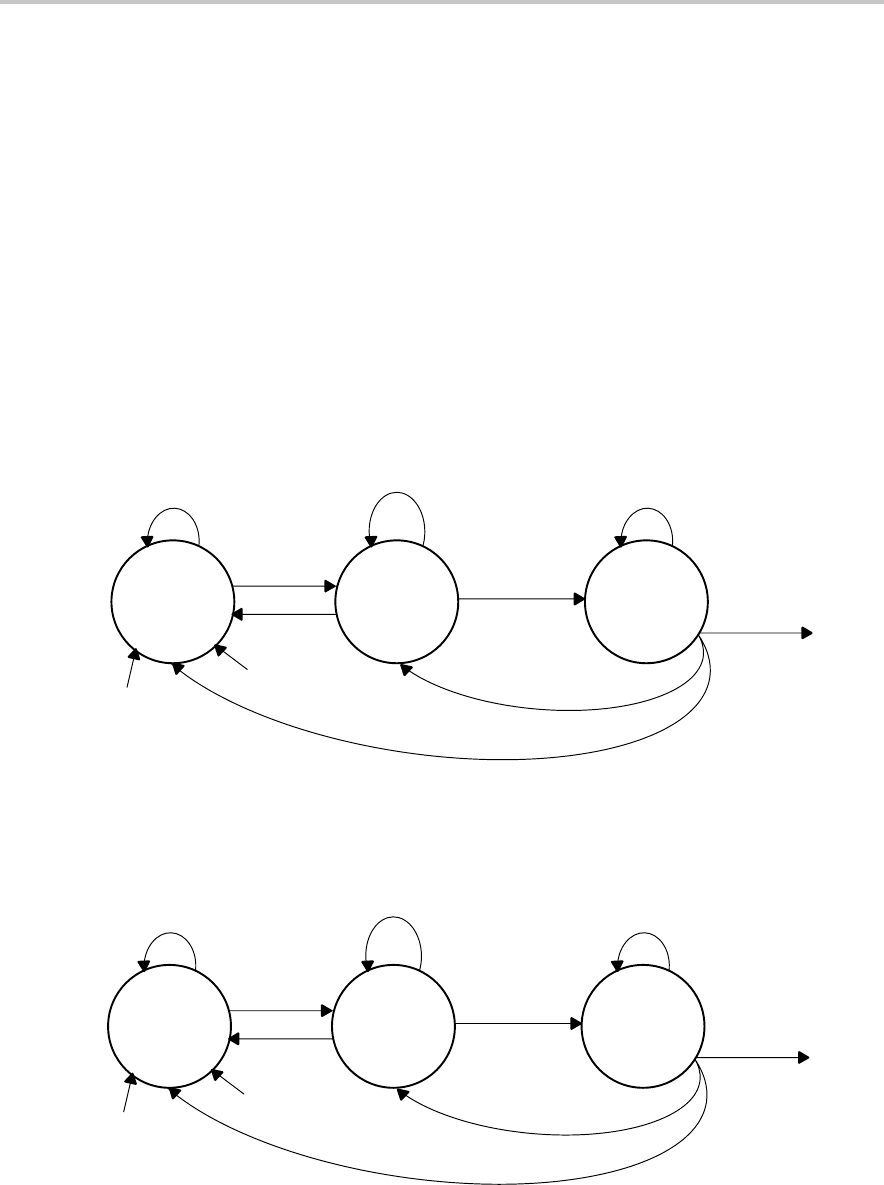

source is active. Figure 15−4 and Figure 15−5 show the transmit enable state

diagrams.

Figure 15−4. Master Mode Transmit Enable

Idle State

(Transmitter

Enabled)

Transmit

Disable

Transmission

Active

USPIEx = 0

No Data Written

to Transfer Buffer

Not Completed

USPIEx = 1

USPIEx = 0

USPIEx = 1,

Data Written to

Transmit Buffer

Handle Interrupt

Conditions

Character

Transmitted

USPIEx = 1

USPIEx = 0 And Last Buffer

Entry Is Transmitted

SWRST

PUC

Figure 15−5. Slave Transmit Enable State Diagram

Idle State

(Transmitter

Enabled)

Transmit

Disable

Transmission

Active

USPIEx = 0

No Clock at UCLK

Not Completed

USPIEx = 1

USPIEx = 0

USPIEx = 1

Handle Interrupt

Conditions

Character

Transmitted

USPIEx = 1

USPIEx = 0

SWRST

PUC

External Clock

Present