DAC12 Operation

23-9DAC12

23.2.6 Grouping Multiple DAC12 Modules

Multiple DAC12s can be grouped together with the DAC12GRP bit to

synchronize the update of each DAC12 output. Hardware ensures that all

DAC12 modules in a group update simultaneously independent of any

interrupt or NMI event.

On the MSP430FG43x devices, DAC12_0 and DAC12_1 are grouped by

setting the DAC12GRP bit of DAC12_0. The DAC12GRP bit of DAC12_1 is

don’t care. When DAC12_0 and DAC12_1 are grouped:

- The DAC12_1 DAC12LSELx bits select the update trigger for both DACs

- The DAC12LSELx bits for both DACs must be > 0

- The DAC12ENC bits of both DACs must be set to 1

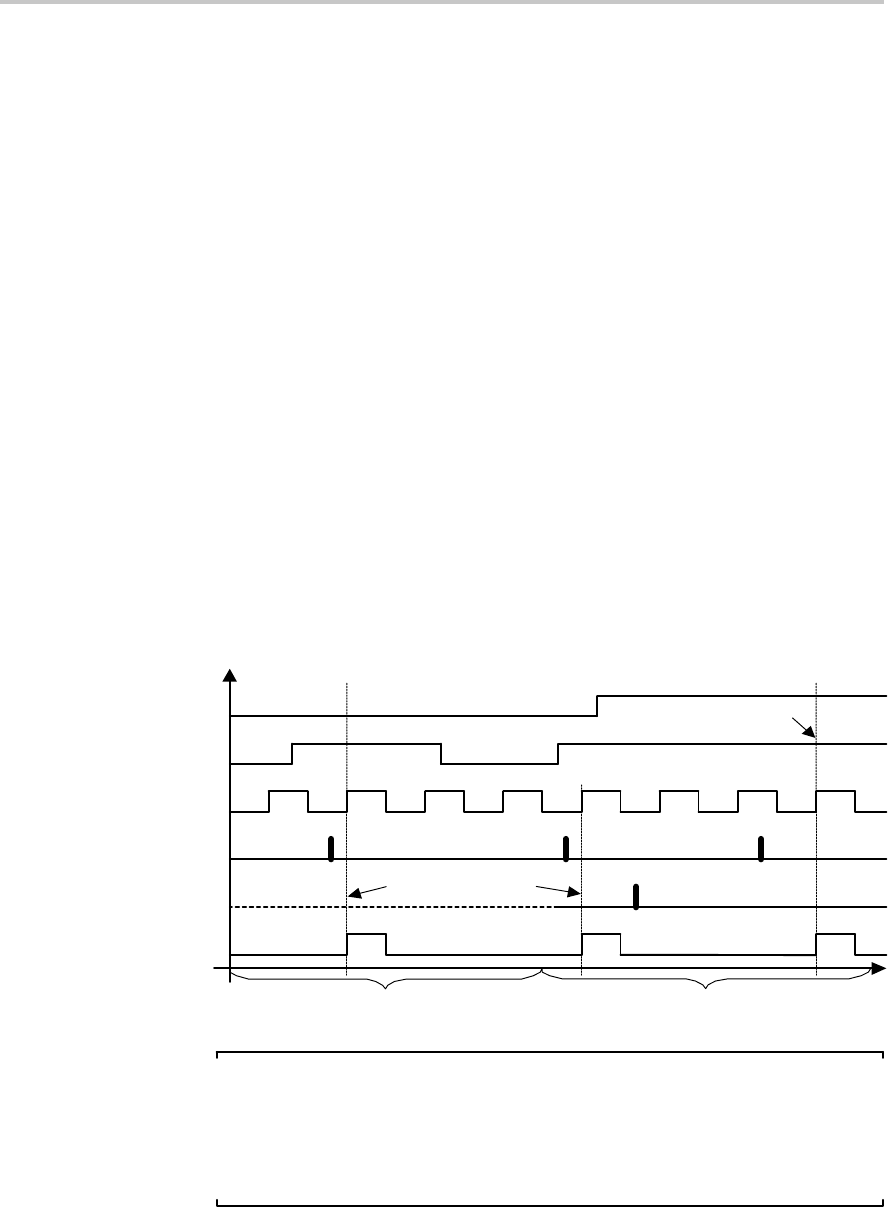

When DAC12_0 and DAC12_1 are grouped, both DAC12_xDAT registers

must be written to before the outputs update - even if data for one or both of

the DACs is not changed. Figure 23−7 shows a latch-update timing example

for grouped DAC12_0 and DAC12_1.

When DAC12_0 DAC12GRP = 1 and both DAC12_x DAC12LSELx > 0 and

either DAC12ENC = 0, neither DAC12 will update.

Figure 23−7. DAC12 Group Update Example, Timer_A3 Trigger

DAC12_0

DAC12GRP

DAC12_0

DAC12ENC

TimerA_OUT1

DAC12_0

Latch Trigger

DAC12_0 Updated

DAC12_0 DAC12LSELx = 2 DAC12_0 DAC12LSELx > 0 AND

DAC12_1 DAC12LSELx = 2

DAC12_0DAT

New Data

DAC12_1DAT

New Data

DAC12_0 and DAC12_1

Updated Simultaneously

Note: DAC12 Settling Time

The DMA controller is capable of transferring data to the DAC12 faster than

the DAC12 output can settle. The user must assure the DAC12 settling time

is not violated when using the DMA controller. See the device-specific data

sheet for parameters.