Scan IF Registers

24-46 Scan IF

SIFCTL4, Scan IF Control Register 4

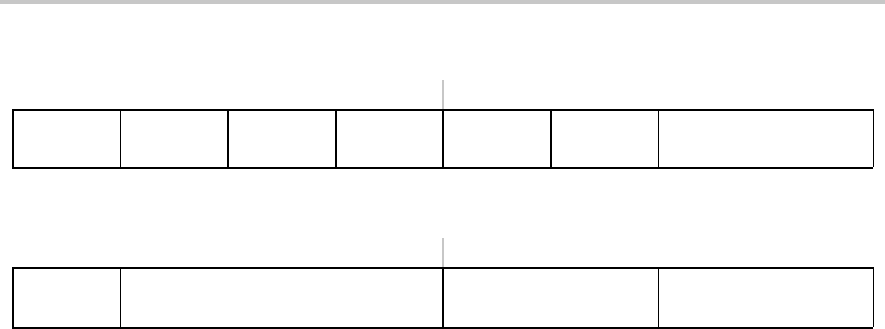

15 14 13 12 11 10 9 8

SIFCNTRST SIFCNT2EN

SIFCNT1

ENM

SIFCNT1

ENP

SIFQ7EN SIFQ6EN SIFDIV3Bx

rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0)

76543210

SIFDIV3Bx SIFDIV3Ax SIFDIV2x SIFDIV1x

rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0) rw−(0)

SIFCNTRST

Bit 15 Counter reset. Setting this bit enables the SIFCNT register to be reset when

it is read.

0 SIFCNT register is not reset when read

1 SIFCNT register is reset when it is read

SIFCNT2EN

Bit 14 SIFCNT2 enable

0 SIFCNT2 is disabled

1 SIFCNT2 is enabled

SIFCNT1

ENM

Bit 13 SIFCNT1 decrement enable

0 SIFCNT1 decrement is disabled

1 SIFCNT1 decrement is enabled

SIFCNT1

ENP

Bit 12 SIFCNT1 increment enable

0 SIFCNT1 increment is disabled

1 SIFCNT1 increment is enabled

SIFQ7EN

Bit 11 Q7 enable. This bit enables bit Q7 for the next PSM state calculation when

SIFQ6EN = 1.

0 Q7 is not used to determine the next PSM state

1 Q7 is used to determine the next PSM state

SIFQ6EN

Bit 10 Q7 enable. This bit enables Q6 for the next PSM state calculation.

0 Q6 is not used to determine the next PSM state

1 Q6 is used to determine the next PSM state