Instruction Set

3-59

RISC 16−Bit CPU

* RLC[.W] Rotate left through carry

* RLC.B Rotate left through carry

Syntax RLC dst or RLC.W dst

RLC.B dst

Operation C <− MSB <− MSB−1 .... LSB+1 <− LSB <− C

Emulation ADDC dst,dst

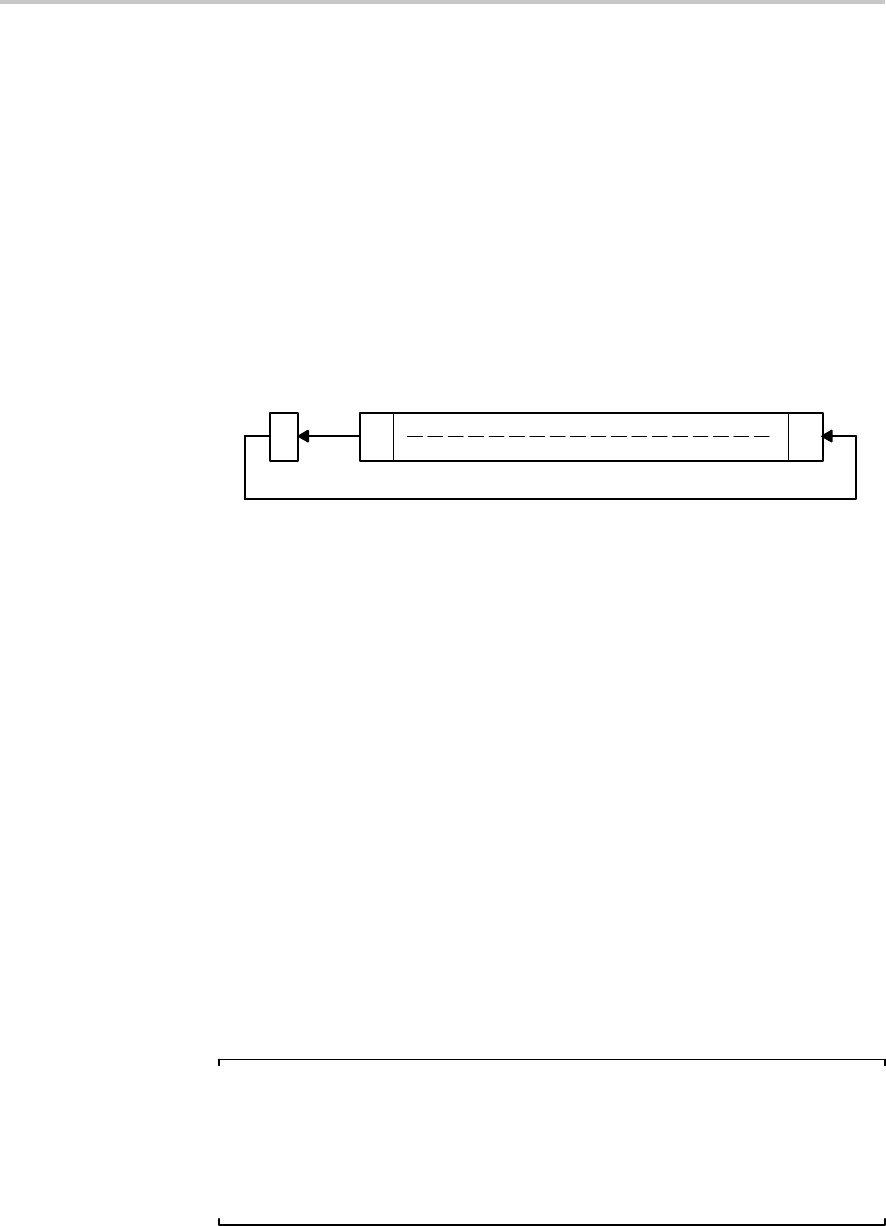

Description The destination operand is shifted left one position as shown in Figure 3−15.

The carry bit (C) is shifted into the LSB and the MSB is shifted into the carry

bit (C).

Figure 3−15. Destination Operand—Carry Left Shift

15 0

70

C

Byte

Word

Status Bits N: Set if result is negative, reset if positive

Z: Set if result is zero, reset otherwise

C: Loaded from the MSB

V: Set if an arithmetic overflow occurs

the initial value is 04000h ≤ dst < 0C000h; reset otherwise

Set if an arithmetic overflow occurs:

the initial value is 040h ≤ dst < 0C0h; reset otherwise

Mode Bits OSCOFF, CPUOFF, and GIE are not affected.

Example R5 is shifted left one position.

RLC R5 ; (R5 x 2) + C −> R5

Example The input P1IN.1 information is shifted into the LSB of R5.

BIT.B #2,&P1IN ; Information −> Carry

RLC R5 ; Carry=P0in.1 −> LSB of R5

Example The MEM(LEO) content is shifted left one position.

RLC.B LEO ; Mem(LEO) x 2 + C −> Mem(LEO)

Note: RLC and RLC.B Substitution

The assembler does not recognize the instruction:

RLC @R5+.

It must be substituted by:

ADDC @R5+,−2(R5).