Address Space

1-4 Introduction

1.4 Address Space

The MSP430 von-Neumann architecture has one address space shared with

special function registers (SFRs), peripherals, RAM, and Flash/ROM memory

as shown in Figure 1−2. See the device-specific data sheets for specific

memory maps. Code access are always performed on even addresses. Data

can be accessed as bytes or words.

The addressable memory space is 64 KB with future expansion planned.

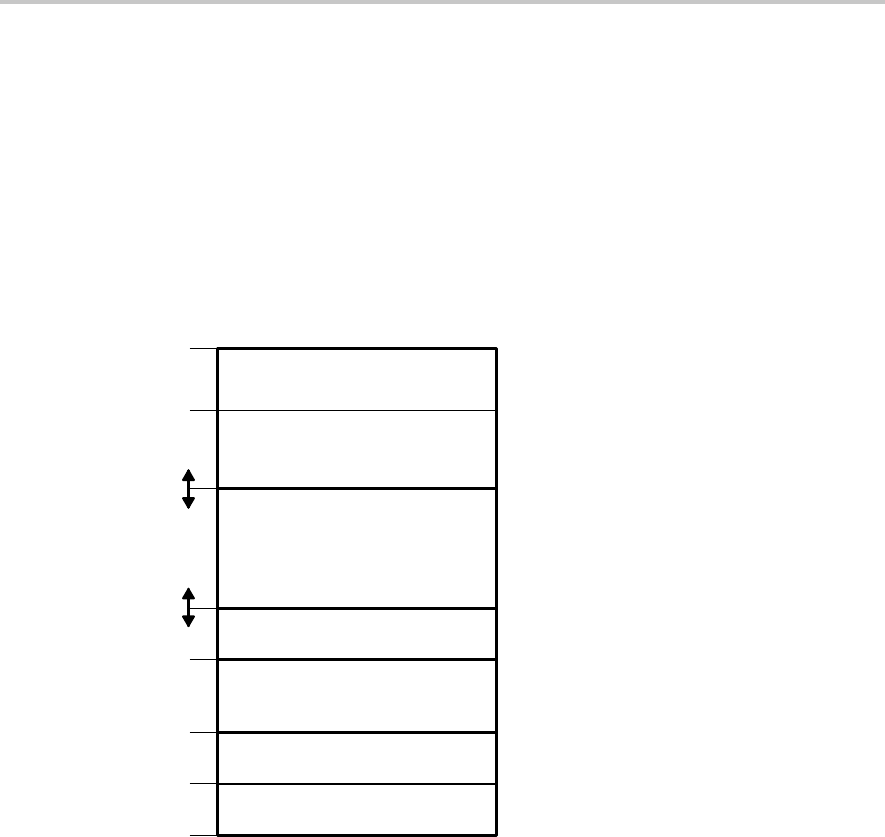

Figure 1−2. Memory Map

0FFE0h

Interrupt Vector Table

Flash/ROM

RAM

16-Bit Peripheral Modules

8-Bit Peripheral Modules

Special Function Registers

0FFFFh

0FFDFh

0200h

01FFh

0100h

0FFh

010h

0Fh

0h

Access

Word/Byte

Word/Byte

Word

Byte

Byte

Word/Byte

1.4.1 Flash/ROM

The start address of Flash/ROM depends on the amount of Flash/ROM

present and varies by device. The end address for Flash/ROM is 0FFFFh.

Flash can be used for both code and data. Word or byte tables can be stored

and used in Flash/ROM without the need to copy the tables to RAM before

using them.

The interrupt vector table is mapped into the upper 16 words of Flash/ROM

address space, with the highest priority interrupt vector at the highest

Flash/ROM word address (0FFFEh).

1.4.2 RAM

RAM starts at 0200h. The end address of RAM depends on the amount of RAM

present and varies by device. RAM can be used for both code and data.