SD16_A Operation

22-7SD16_A

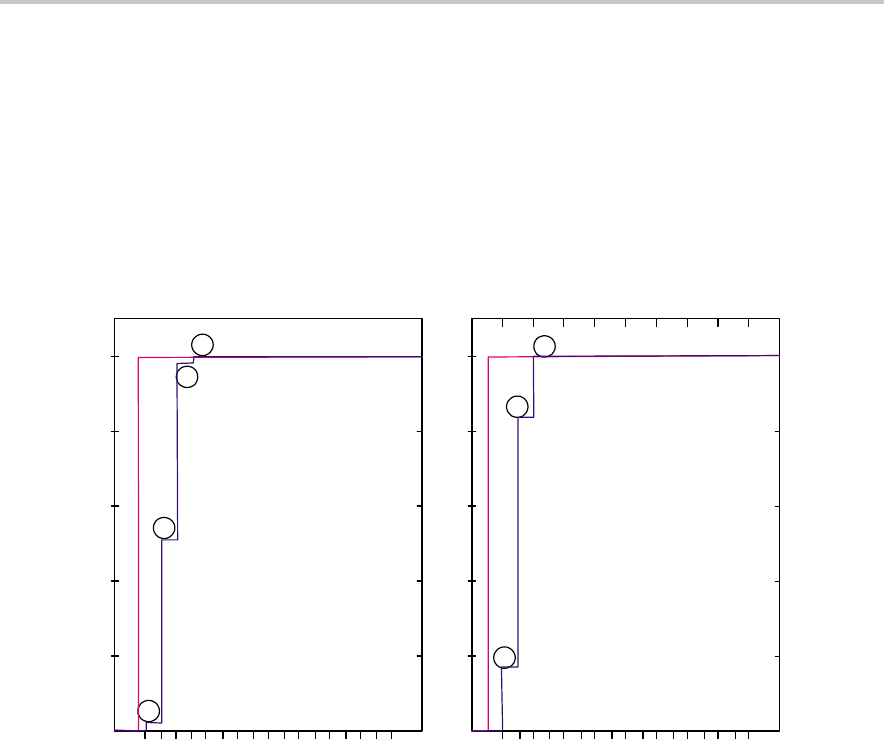

Figure 22−3 shows the digital filter step response and conversion points. For

step changes at the input after start of conversion a settling time must be

allowed before a valid conversion result is available. The SD16INTDLYx bits

can provide sufficient filter settling time for a full-scale change at the ADC

input. If the step occurs synchronously to the decimation of the digital filter the

valid data will be available on the third conversion. An asynchronous step will

require one additional conversion before valid data is available.

Figure 22−3. Digital Filter Step Response and Conversion Points

1

2

3

4

1

0

0.2

0.4

0.6

0.8

1

0

0.2

0.4

0.6

0.8

1

2

3

Asynchronous Step Synchronous Step

% V

FSR

Conversion Conversion